Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as device performance degradation, high contact plug resistance, reliability problems, etc., to reduce parasitic Effects of resistance, performance improvement, and high conductivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

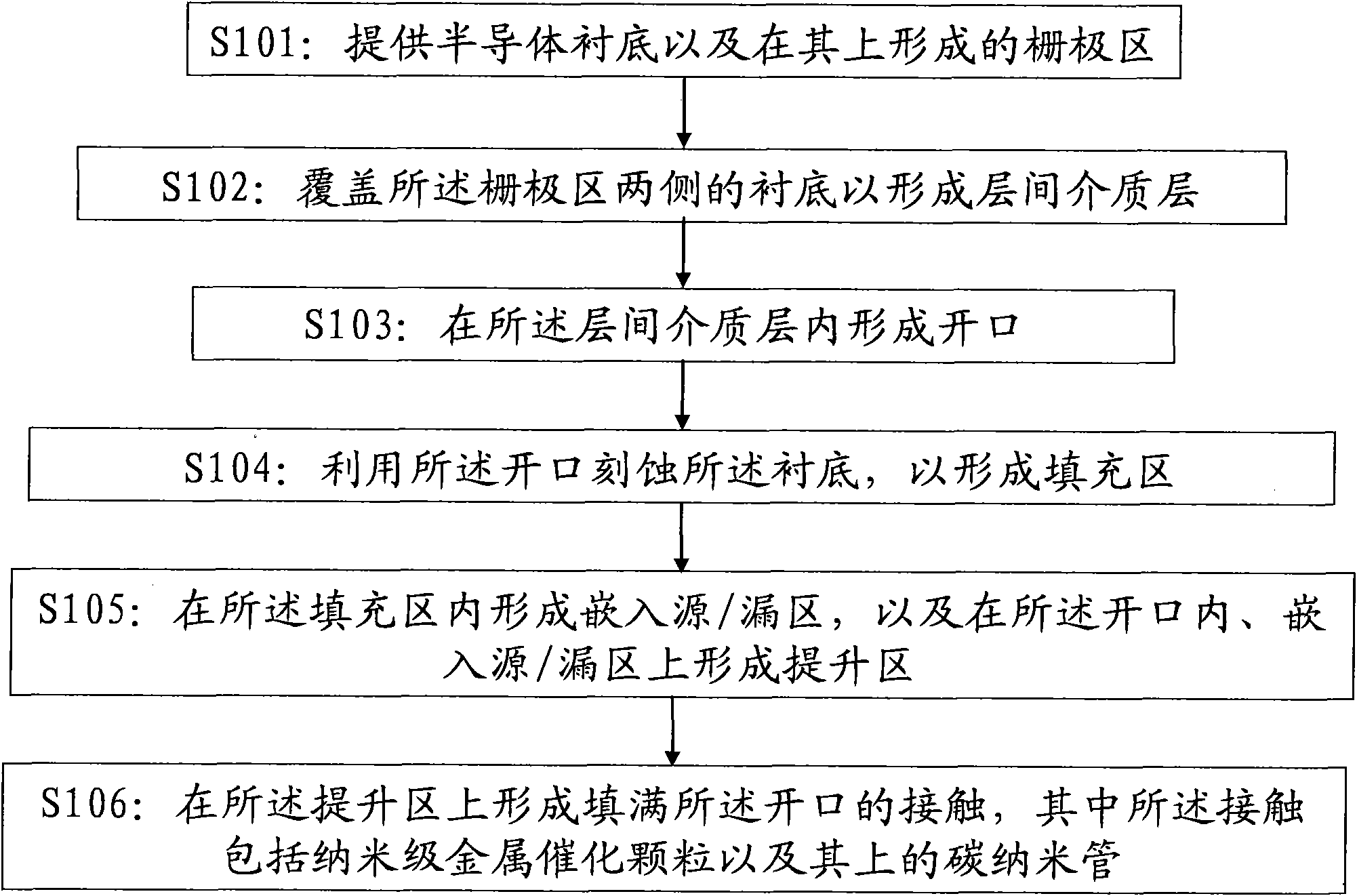

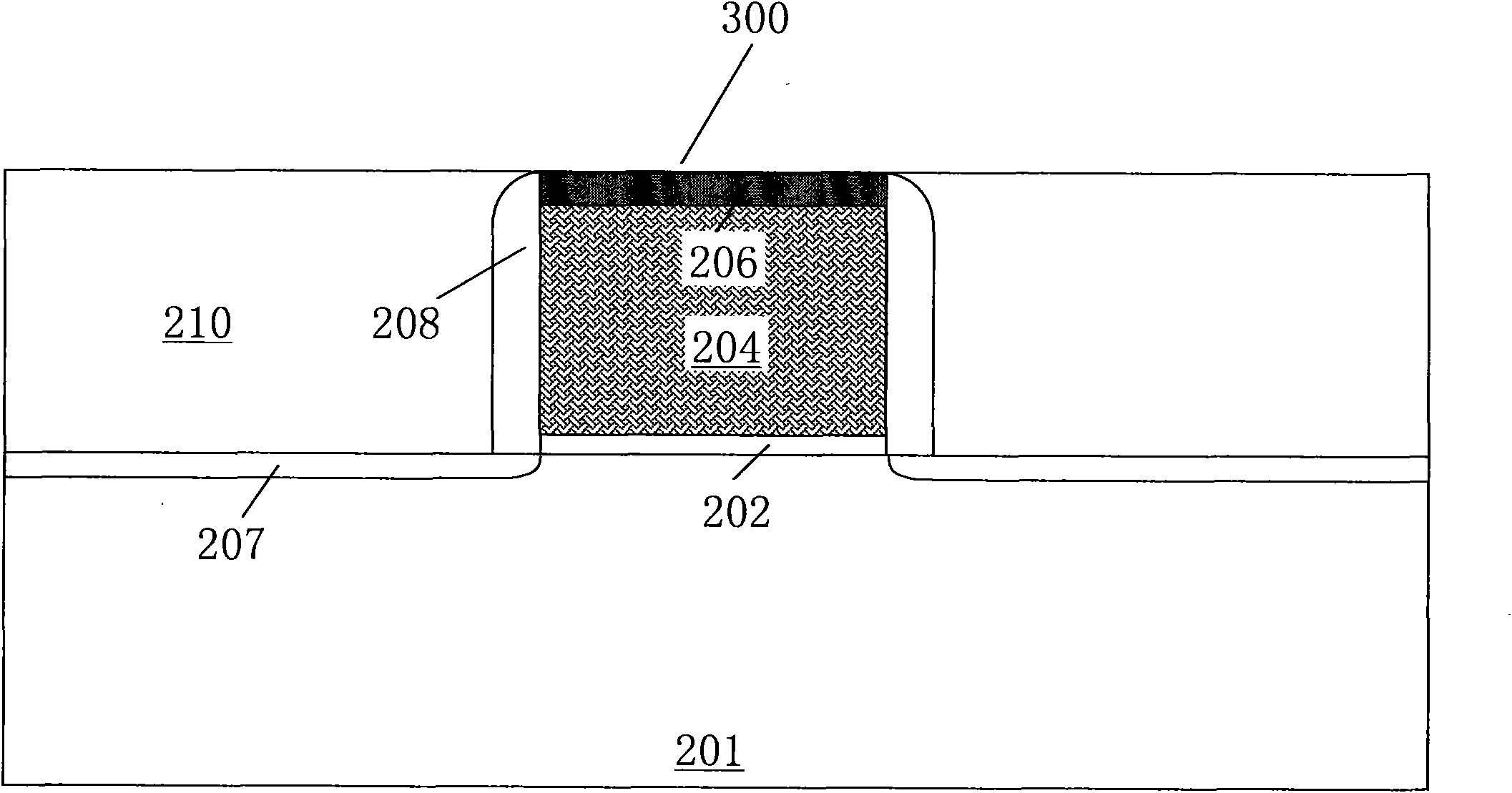

[0015] refer to figure 1 , figure 1 A flowchart of a method for manufacturing a semiconductor device according to a first embodiment of the present invention is shown. In step S101, a semiconductor substrate 201 and a gate region 300 formed thereon are provided, refer to figure 2 . In this embodiment, the substrate 201 has been pre-processed, and the processing operations include pre-cleaning, forming a well region and forming a shallow trench isolation region. In this embodiment, the substrate 201 is silicon The substrate. In other embodiments, the substrate 201 may also include other compound semiconductors, such as silicon carbide, gallium arsenide, indium arsenide or indium phosphide. The substrate 201 may include various doping configurations according to design requirements known in the art (eg, p-type substrate or n-type substrate). In addition, preferably, the substrate 201 includes an epitaxial layer, and the substrate 201 may also include a silicon-on-insulator ...

no. 2 example

[0023] Only the aspects of the second embodiment that differs from the first embodiment will be described below. Parts not described should be considered to be performed using the same steps, methods or processes as those in the first embodiment, so details will not be repeated here.

[0024] refer to Figure 10 , Figure 10 A flowchart of a method for manufacturing a semiconductor device according to a second embodiment of the present invention is shown. In step S201, a semiconductor substrate 201 and a gate region 300 formed thereon are provided, and source / drain doped regions 216 are formed in the substrate on both sides of the gate region, refer to Figure 11 . The substrate 201 and the gate region 300 are the same as those in the first embodiment, and will not be repeated here. The source / drain doped region 216 can be formed by implanting p-type or n-type dopants or impurities into the substrate 200 according to the desired transistor structure, which can be formed by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com