Dynamic delay, and phase-frequency detector (PFD) and phase lock loop adopting same

A frequency discriminator, dynamic delay technology, applied in the direction of automatic power control, electrical components, etc., can solve problems such as dead zone, and achieve the effect of removing dead zone, overcoming process deviation, and high practical value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

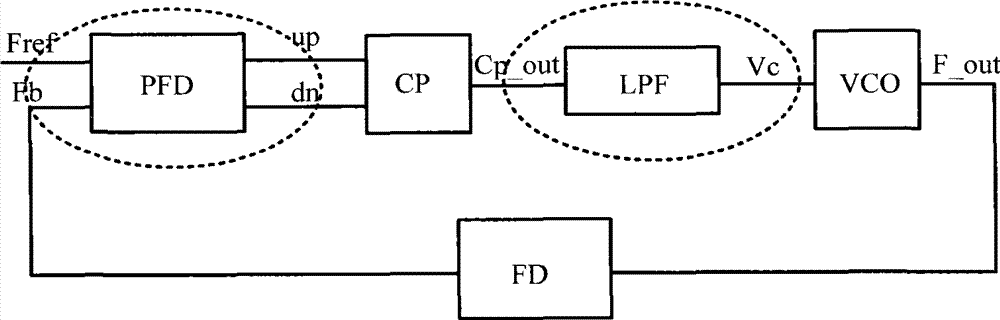

[0032] In this embodiment, a dynamic delayer is used in the PFD of the PLL, which can overcome the PFD dead zone phenomenon caused by the process, temperature, etc. according to the preset delay time; and integrate a resonant circuit in the original passive LPF, which can target the input The frequency of the clock can greatly suppress the stray signal brought in by the input terminal and optimize the system performance.

[0033] The specific implementation will be described in detail below in conjunction with the accompanying drawings.

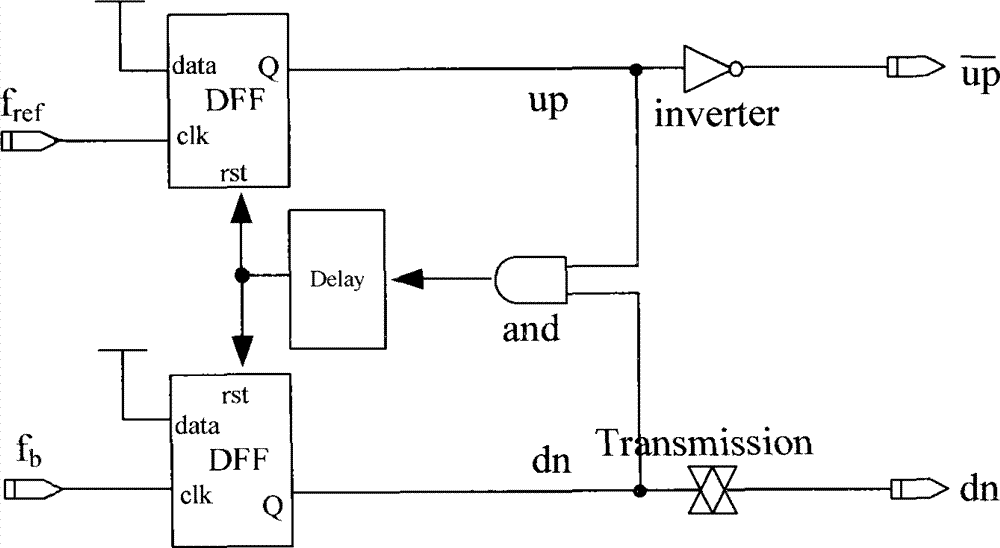

[0034] figure 2 The structure of the existing PFD includes: two flip-flops, a delayer, an AND gate, an inverter and a transmission gate, and the data input terminal (clk) of the first flip-flop is connected to the reference signal f ref , clk of the second flip-flop is connected to the feedback signal f b , the output (Q) end of the first flip-flop is respectively connected to the inverter and one input end of the AND gate, the Q end of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com