Estimation method and system of clock tree delay time in specified integrated circuit

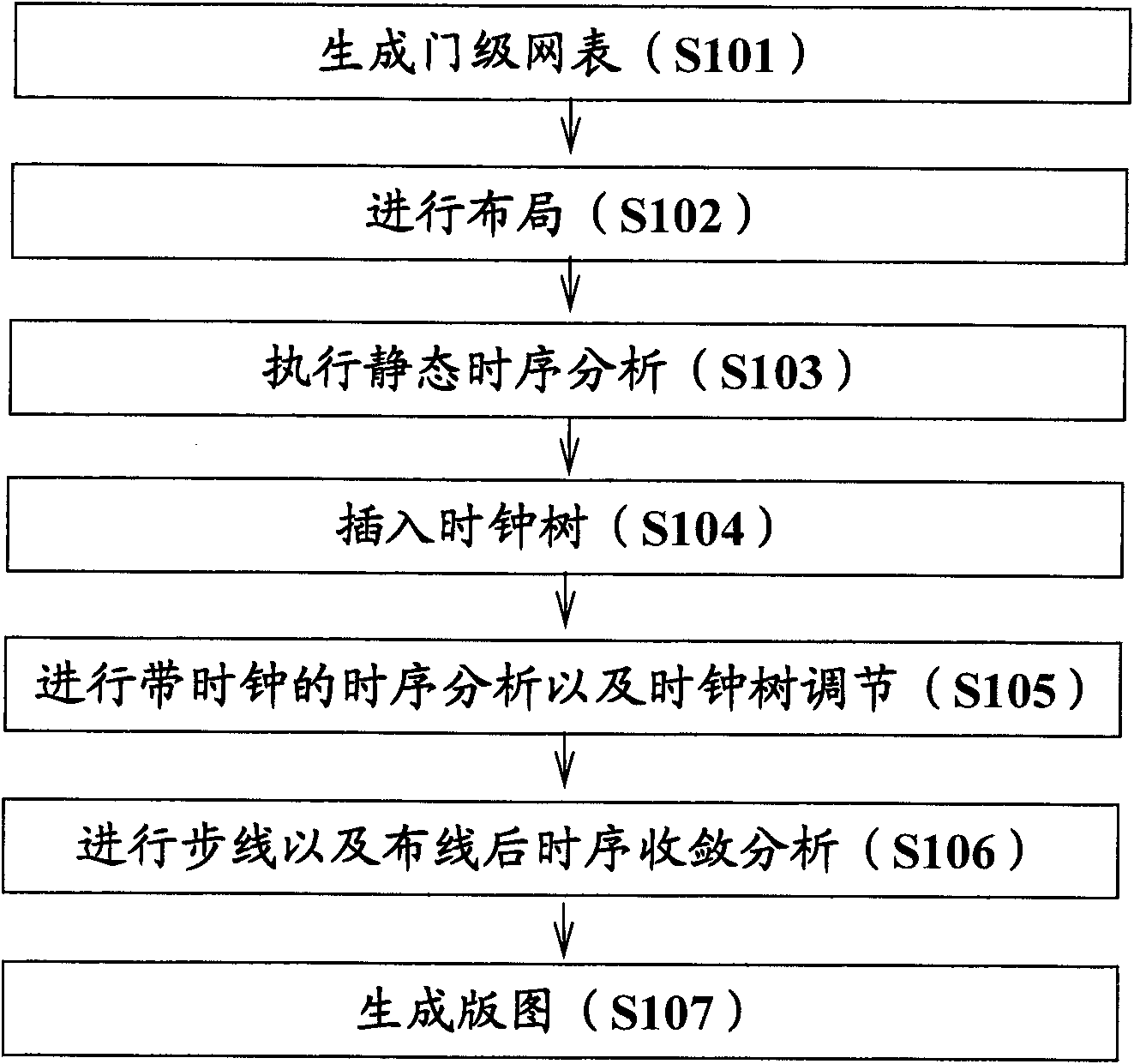

An integrated circuit and delay time technology, which is applied in the field of estimation of time tree delay time and clock signal arrival time, can solve the problems of prolonging the design cycle, time-consuming clock tree insertion, long product design cycle, etc., so as to reduce design time and improve The effect of design efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

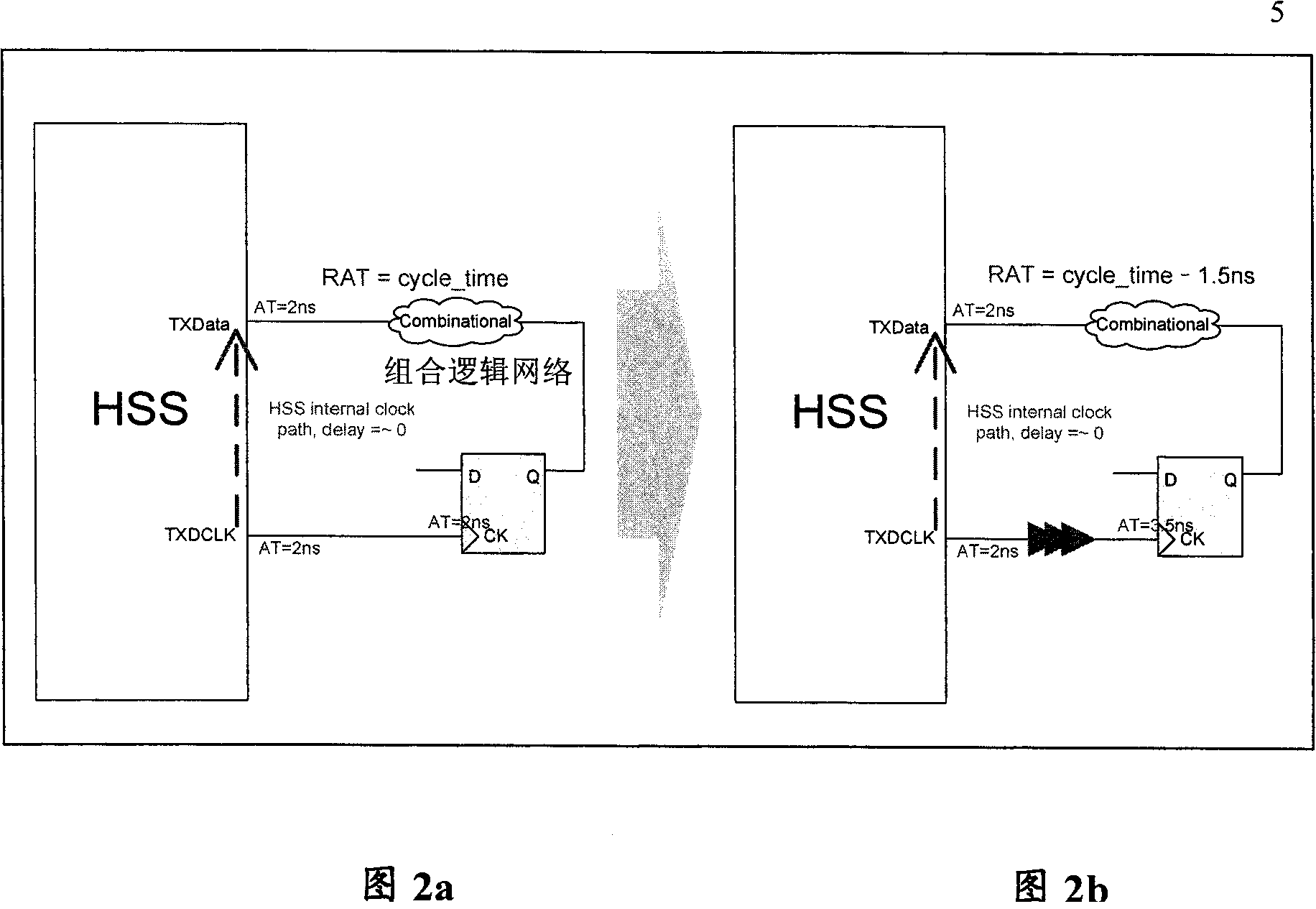

Embodiment Construction

[0041] The preferred embodiments of the present invention will be described in more detail with reference to the accompanying drawings, in which the preferred embodiments of the present invention are shown. However, the present invention can be implemented in various forms and should not be construed as being limited by the embodiments set forth herein. On the contrary, these embodiments are provided to make the present invention more thorough and complete, and to fully convey the scope of the present invention to those skilled in the art.

[0042] First clarify some basic concepts for the description of the invention later.

[0043] Netlist: A file or data structure that expresses the topological connection of a digital circuit device, and does not contain the physical information of the device (for example, the physical location and orientation of the device).

[0044] Layout: A file or data structure that expresses physical location information (such as physical location, orienta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com