Multilayer wiring substrate

A multi-layer wiring substrate and copper layer technology, applied to electrical components, printed circuit components, printed circuits, etc., can solve problems such as insufficient connection strength and achieve reliable connection effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

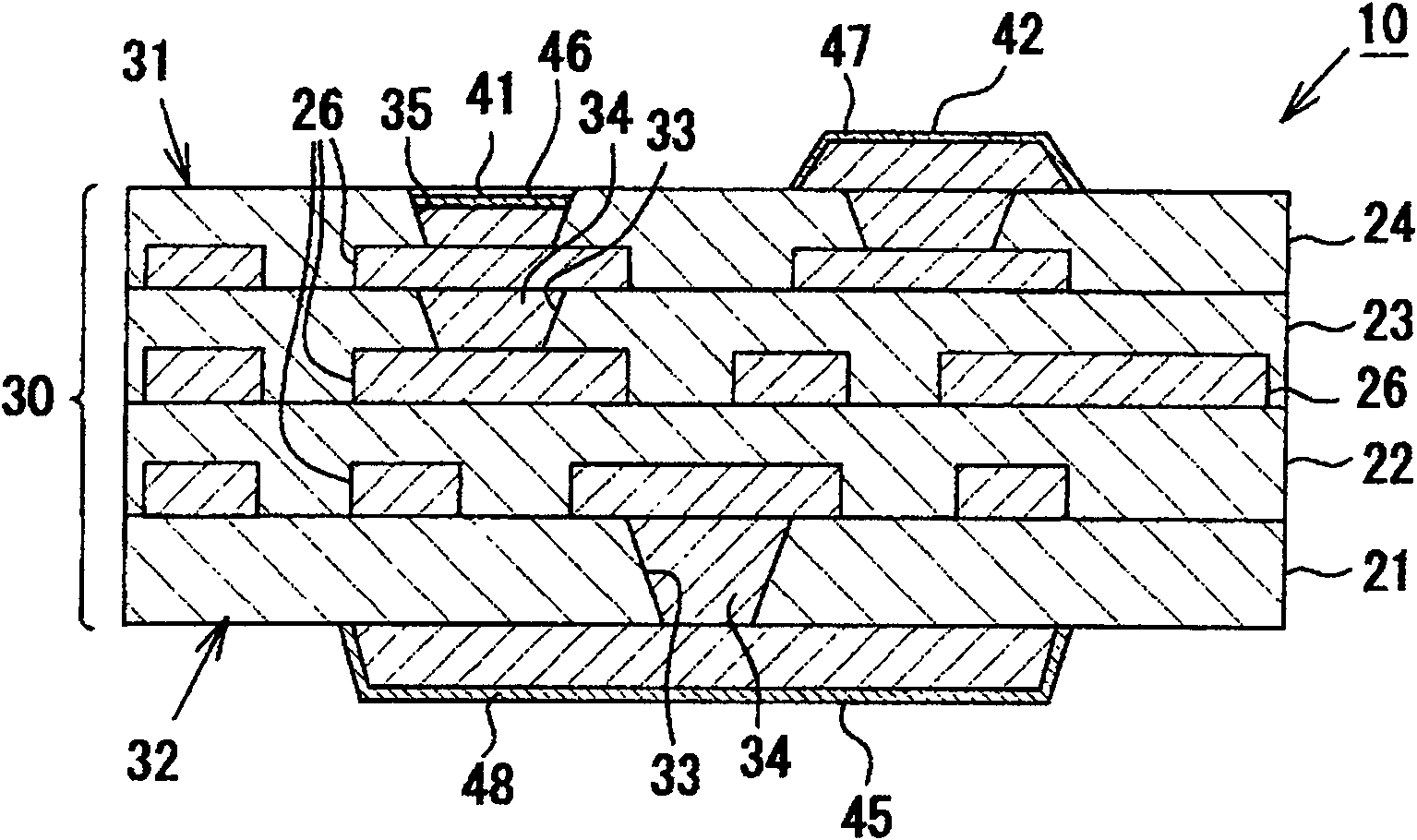

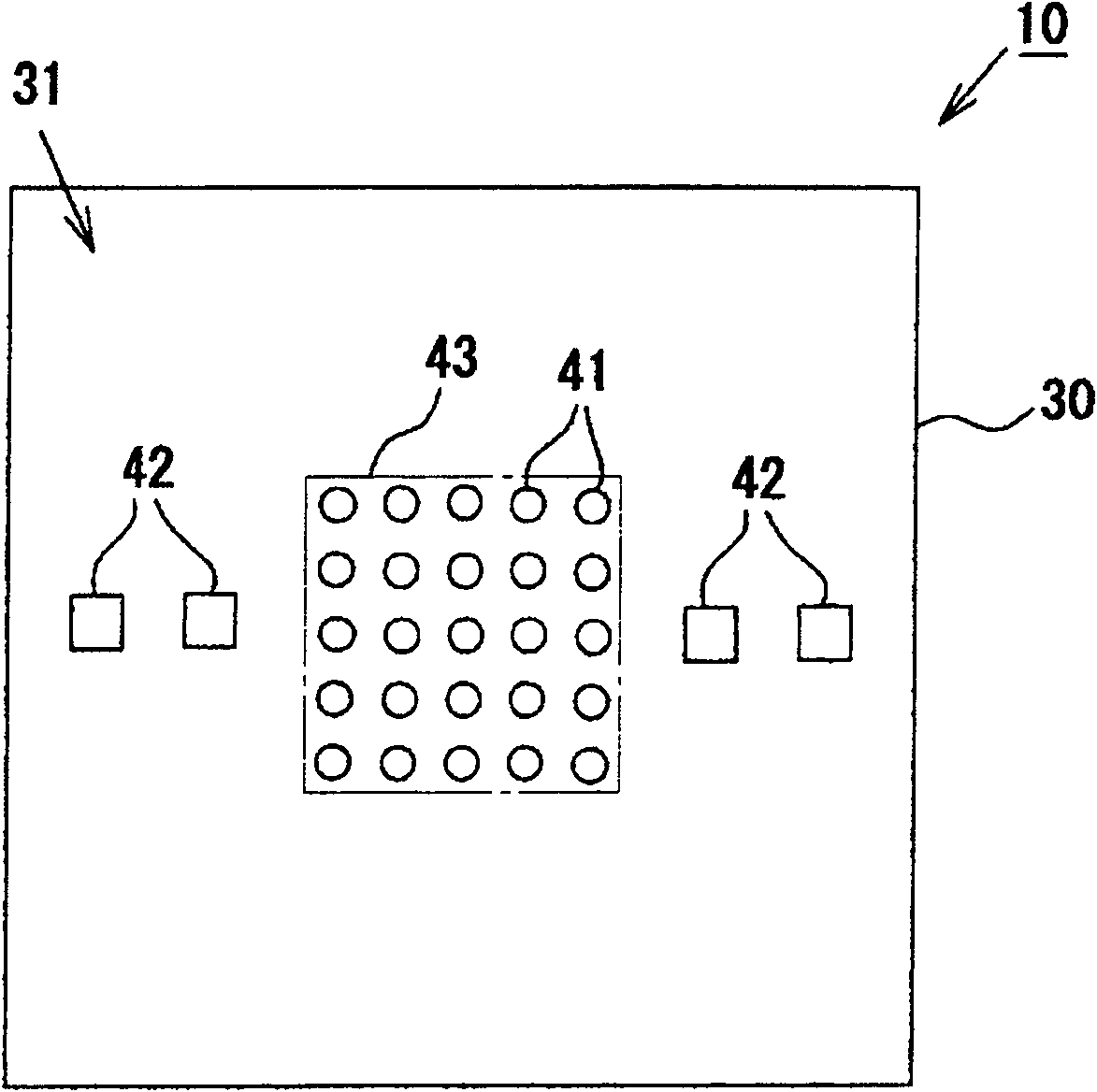

[0063] Hereinafter, a first embodiment in which the present invention is embodied as a multilayer wiring board will be described in detail with reference to the drawings. figure 1 is an enlarged cross-sectional view showing an outline of the structure of the multilayer wiring board according to the present embodiment, figure 2 is a plan view of the multilayer wiring board.

[0064] Such as figure 1 As shown, the multilayer wiring substrate 10 is a coreless wiring substrate formed without a core substrate, and has a wiring laminated portion 30 (laminated structure), which is composed of four resin insulating layers 21 mainly made of the same resin insulating material, 22 , 23 , 24 and the conductor layer 26 made of copper are alternately stacked in a multi-layered wiring laminated portion. Each of the resin insulating layers 21 to 24 is formed using a composite material mainly composed of a non-photocurable resin insulating material, specifically, a cured product of a thermo...

no. 2 Embodiment approach

[0098] Next, a second embodiment of the present invention will be described with reference to the drawings. Such as Figure 16 As shown, in the multilayer wiring board 10A of this embodiment, the shapes and manufacturing methods of the IC chip connection terminals 41A and capacitor connection terminals 42A formed on the upper surface 31 side of the wiring lamination portion 30 are the same as those of the above-mentioned first embodiment. different. The differences from the first embodiment will be described below focusing on the differences.

[0099] Such as Figure 16 As shown, in the multilayer wiring board 10A, no filled via conductor is formed in the opening 35 of the outermost resin insulating layer 24, and the height of the upper surface of the IC chip connection terminal 41A formed in the opening 35 is The height is substantially the same as that of the conductor layer 26 formed on the base pattern layer (resin insulating layer 23 ). In addition, a plated layer 46 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com