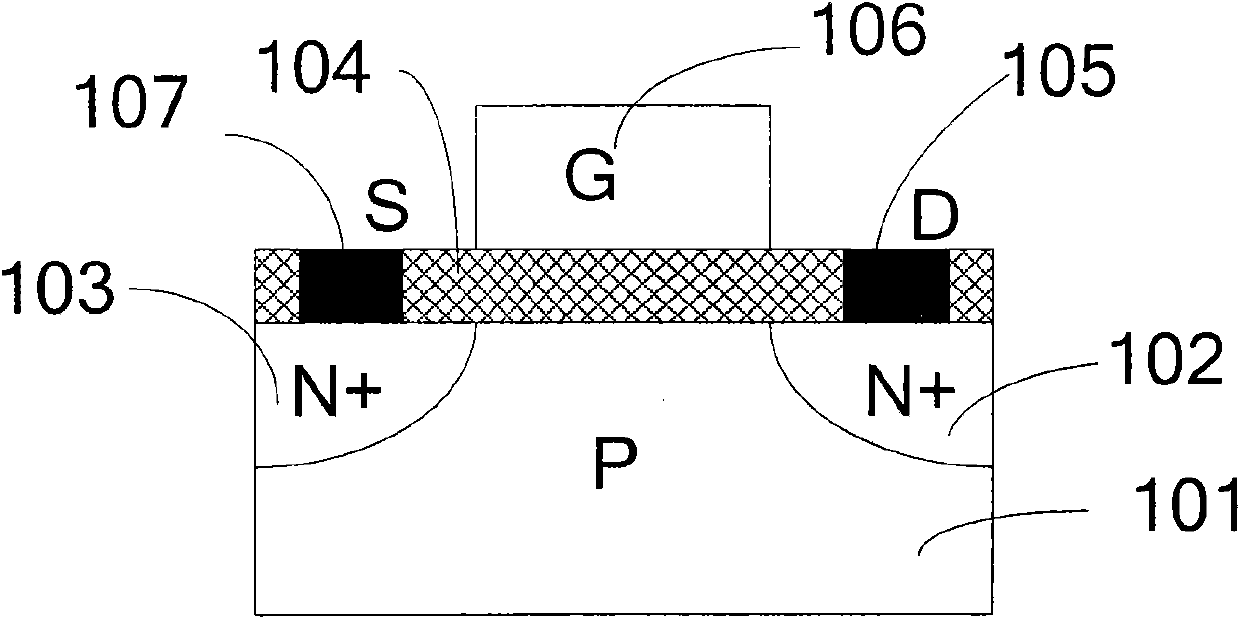

Metal oxide semiconductor field effect transistor and manufacturing method thereof

An oxide semiconductor and field effect transistor technology, which is applied in the field of improving metal oxide semiconductor field effect transistors and their manufacturing, and can solve the problems of high thermal stress, increased connection leakage rate, and decreased device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

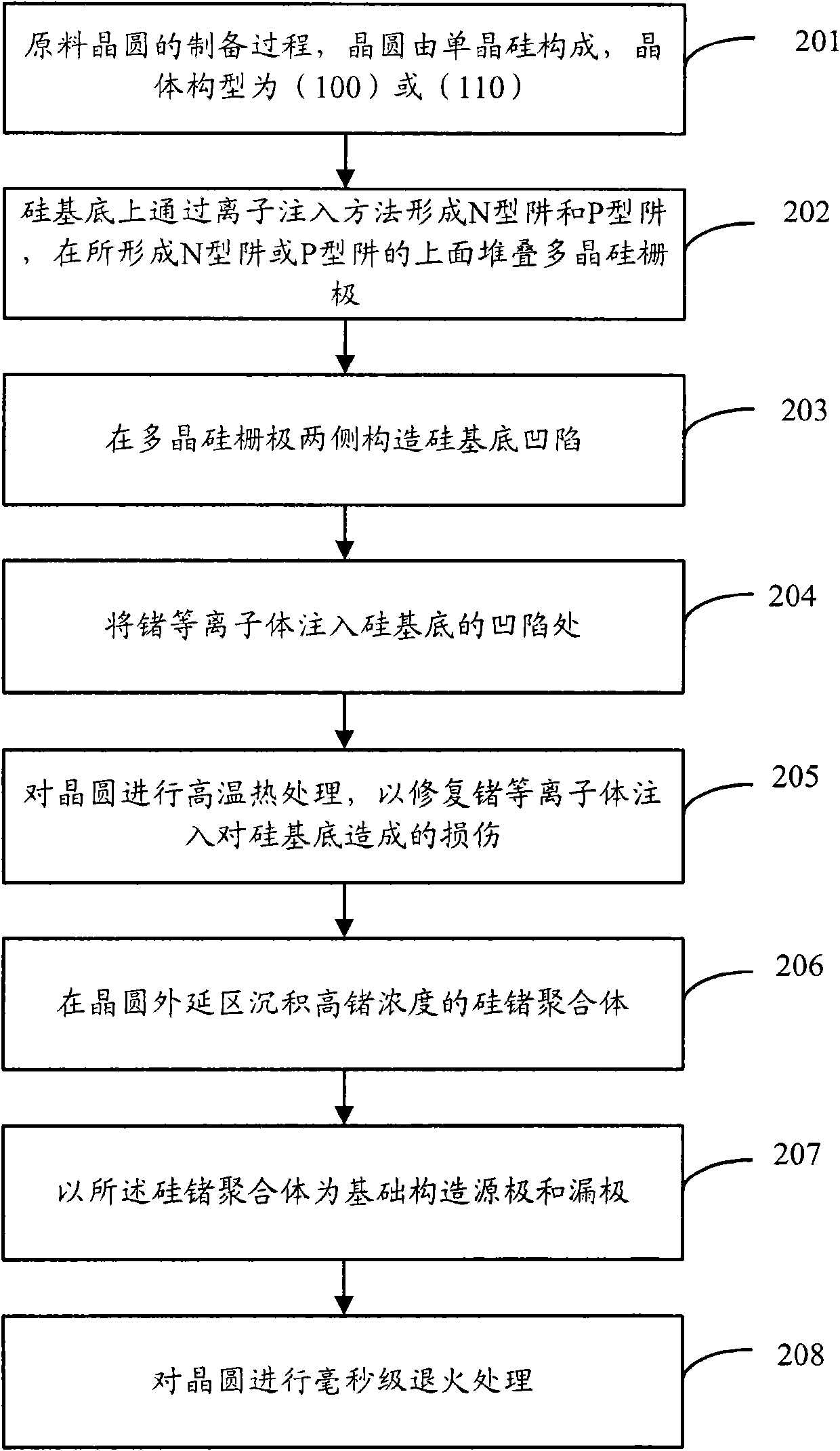

Embodiment Construction

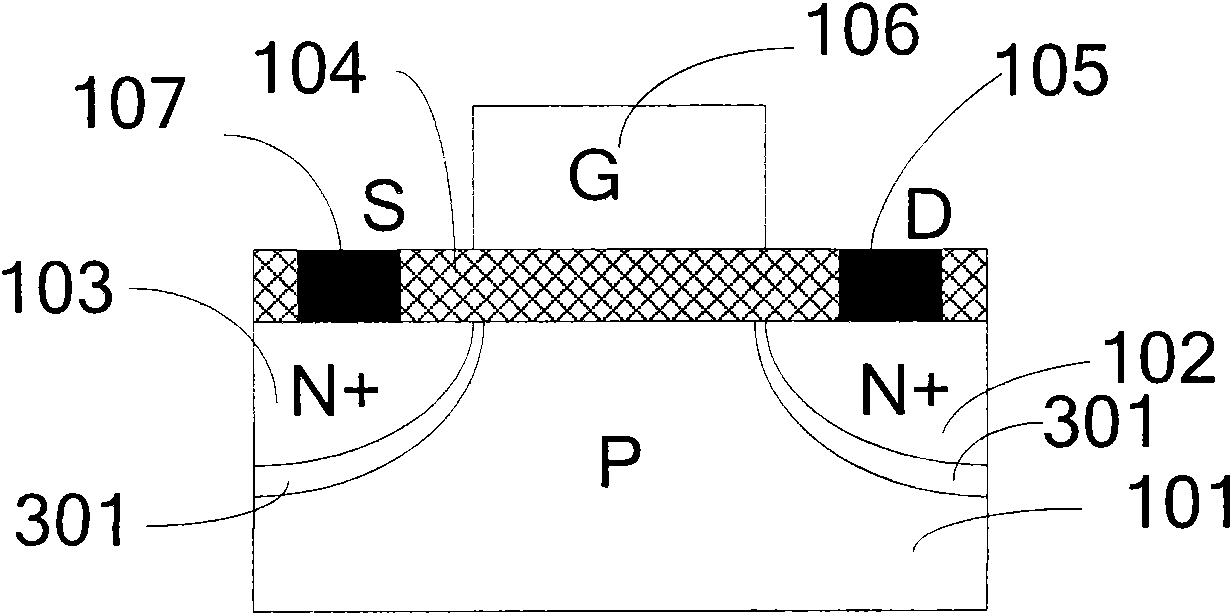

[0030] The root cause of SiGe stress relaxation is the difference in lattice constants between SiGe and Si. The lattice constant of Ge is 5.6 angstroms, the lattice constant of Si is 5.4 angstroms, and the range of the lattice constant of epitaxial SiGe is between 5.4 angstroms and 5.6 angstroms. The higher the Ge concentration, the greater the difference between the lattice constant of SiGe and the lattice constant of Si, and the greater the difference, the greater the stress on the interface between SiGe and Si, and the greater the stress will be. Will cause SiGe stress relaxation.

[0031] Aiming at the root cause of SiGe stress relaxation, the solution adopted by the present invention is to form a buffer layer between SiGe and the silicon substrate. The lattice constant of the buffer layer is close to the lattice constant of Si of 5.4 angstroms on the side close to the Si substrate. The side close to the SiGe layer is close to the lattice constant of SiGe. The internal latt...

PUM

| Property | Measurement | Unit |

|---|---|---|

| lattice constant | aaaaa | aaaaa |

| lattice constant | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com