Interconnection structure, a thin film transistor substrate, and a manufacturing method thereof, as well as a display device

A thin-film transistor and wiring structure technology, which is applied in the manufacture of transistors, semiconductor/solid-state devices, electric solid-state devices, etc., can solve problems such as cost reduction, and achieve the effects of good productivity, enlarged process margin, and excellent contact resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

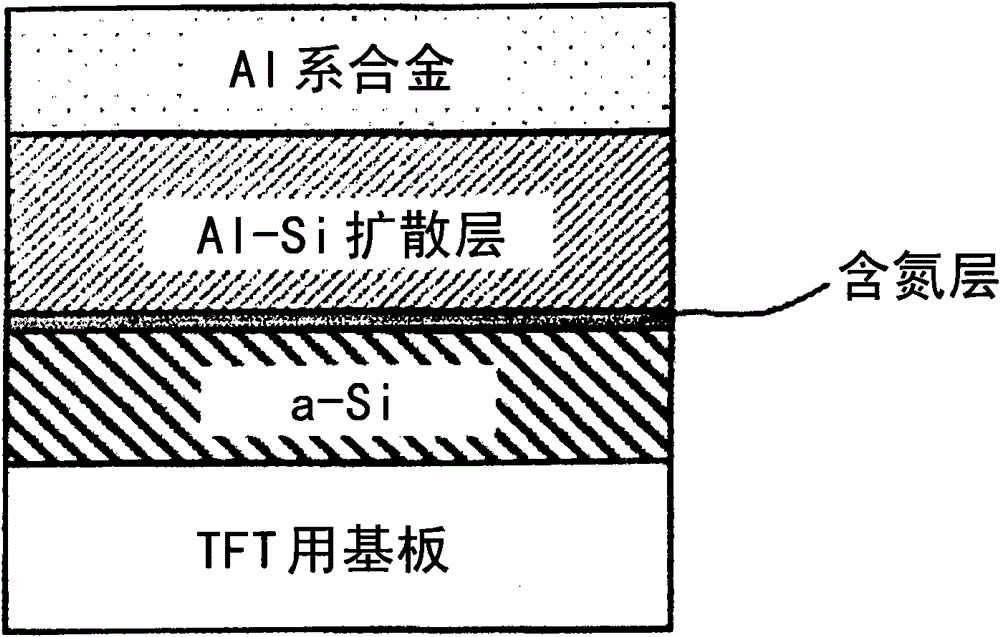

[0066] The first embodiment of the TFT of the present invention is shown in Figure 1A . exist Figure 1A Among them, there is a first semiconductor layer on the TFT substrate, a two-layer laminated structure consisting of (N, C, F) layers and an Al-Si diffusion layer is directly thereon, and a semiconductor layer is formed directly thereon. The structure of the Al alloy layer. Figure 1A The structure of can be obtained by forming the second semiconductor layer after forming the (N, C, F) layer, and then applying a heat treatment of about 150° C. or higher, for example, by the method of Example 1 described later.

[0067] In the first embodiment, the (N, C, F) layer constituting the wiring structure contains any element among nitrogen, carbon, and fluorine. Since the (N, C, F) layer is formed so as to cover almost the entire surface of the semiconductor layer, it is effective as a barrier for preventing interdiffusion of Al and Si at the interface between the Al-based alloy a...

no. 2 Embodiment approach

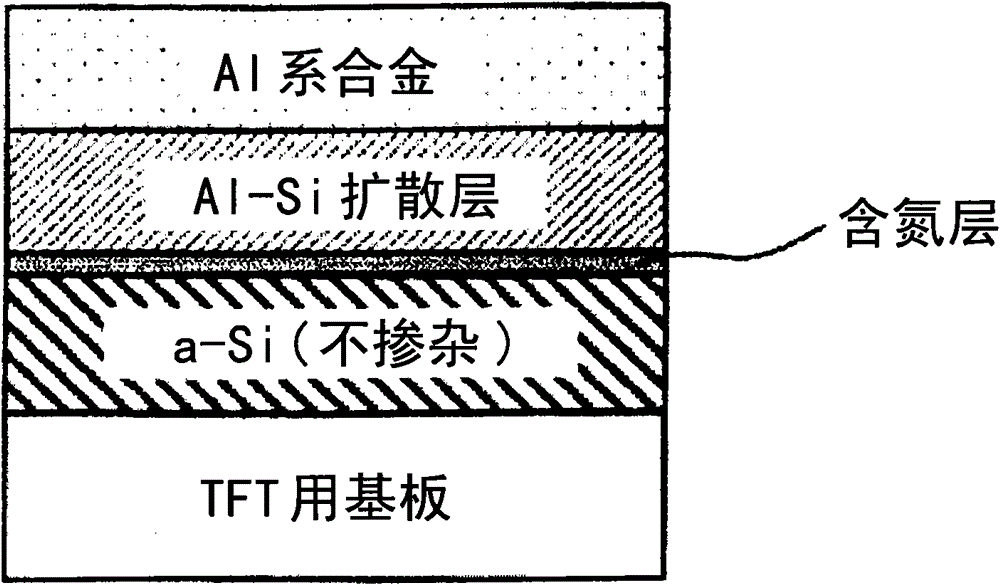

[0099] The second embodiment of the TFT of the present invention is a modified example of the Al-Si diffusion layer in the above-mentioned first embodiment, and has the following figure 2 An example of a 3-layer stack structure is shown. Specifically, since the TFT is manufactured under the condition that the interdiffusion of Al and Si does not proceed to the nitrogen-containing layer, it has a second semiconductor layer that does not substantially contain Al (that is, a semiconductor layer that is substantially only composed of Si). ), (N, C, F) layers, and an Al-Si diffusion layer in the form of a three-layer laminated structure, such a form is also included in the scope of the present invention. Here, "substantially not containing Al" means that the concentration of Al is approximately 0.01 atomic % or less when elemental analysis of Al is performed by the measuring method described later.

[0100] figure 2 The structure can be obtained, for example, by the method of E...

Embodiment approach

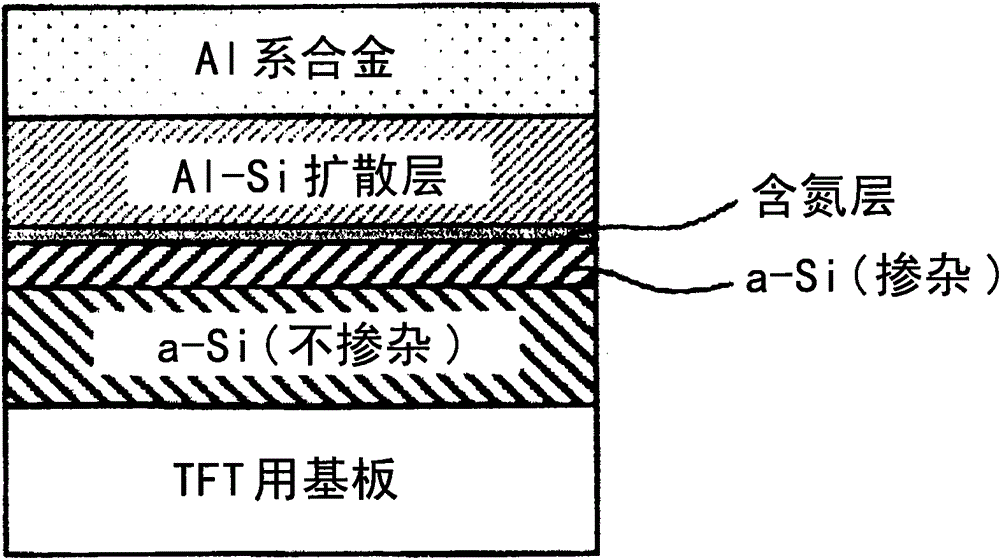

[0102] A third embodiment of the TFT of the present invention has a first semiconductor layer, a (N, C, F) layer, An example of the first semiconductor layer. In detail, it has the following structure, that is, as image 3 As shown, there are a first semiconductor layer, a (N, C, F) layer, and a first semiconductor layer on the TFT substrate, and a (N, C, F) layer and an Al-Si diffusion layer are directly placed on it. A two-layer laminated structure is formed, and an Al-based alloy layer is directly formed on top of it. image 3 The structure of can be obtained by, for example, the method of Example 3 described later. In addition, other conditions, characteristics, etc. are the same as those described in the said 1st Embodiment.

[0103] (the fourth embodiment of the present invention)

[0104] A fourth embodiment of the TFT of the present invention has a first semiconductor layer and a (N, C, F) layer between the nitrogen-containing layer and the TFT substrate constituti...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com