Device for measuring clearance between mask and silicon chip and leveling mask and silicon chip in nanolithography

A nano-lithography and leveling device technology, which is applied in the photolithography exposure device, micro-lithography exposure equipment, optics, etc., to achieve the effects of overcoming system error factors, facilitating optical path adjustment, and strong practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

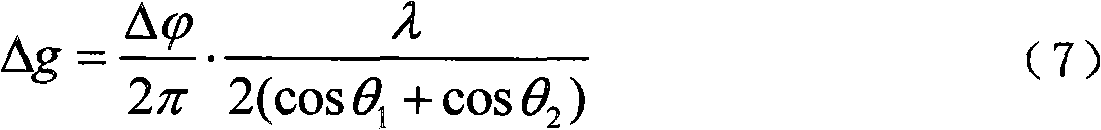

[0026] Such as figure 1 As shown, the plane wave light source with a wavelength of 633nm emitted by the light source laser tube 1 is vertically incident on two groups of adjacent first marking gratings 5 and second marking gratings 6 located in the marking area on the mask 3 after passing through the reflector 2; The diffracted light B transmitted by the first marking grating 5 1 After propagating between the mask and the silicon wafer, and reflected by the surface of the silicon wafer 4 at an angle θ 1 Returning to the surface of the second marking grating 6, with another beam directly from the second marking grating 6 at an angle θ 2 Returned reflected diffracted light B 2 Two beams interfere when they meet on the marked surface, and the two beams of interfering light B 1 and B 2 After being reflected by the mirror 7, it turns back to the horizontal direction and is received by the objective lens 8, so that the interference fringes are recorded by the CCD detector 9 lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com