High-density low-parasitic capacitor

A capacitive device, low parasitic technology, applied in the direction of circuits, electrical components, electric solid-state devices, etc., can solve problems that affect circuit performance and limit applications, and achieve the effect of improving performance, reducing additional power consumption, and achieving remarkable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

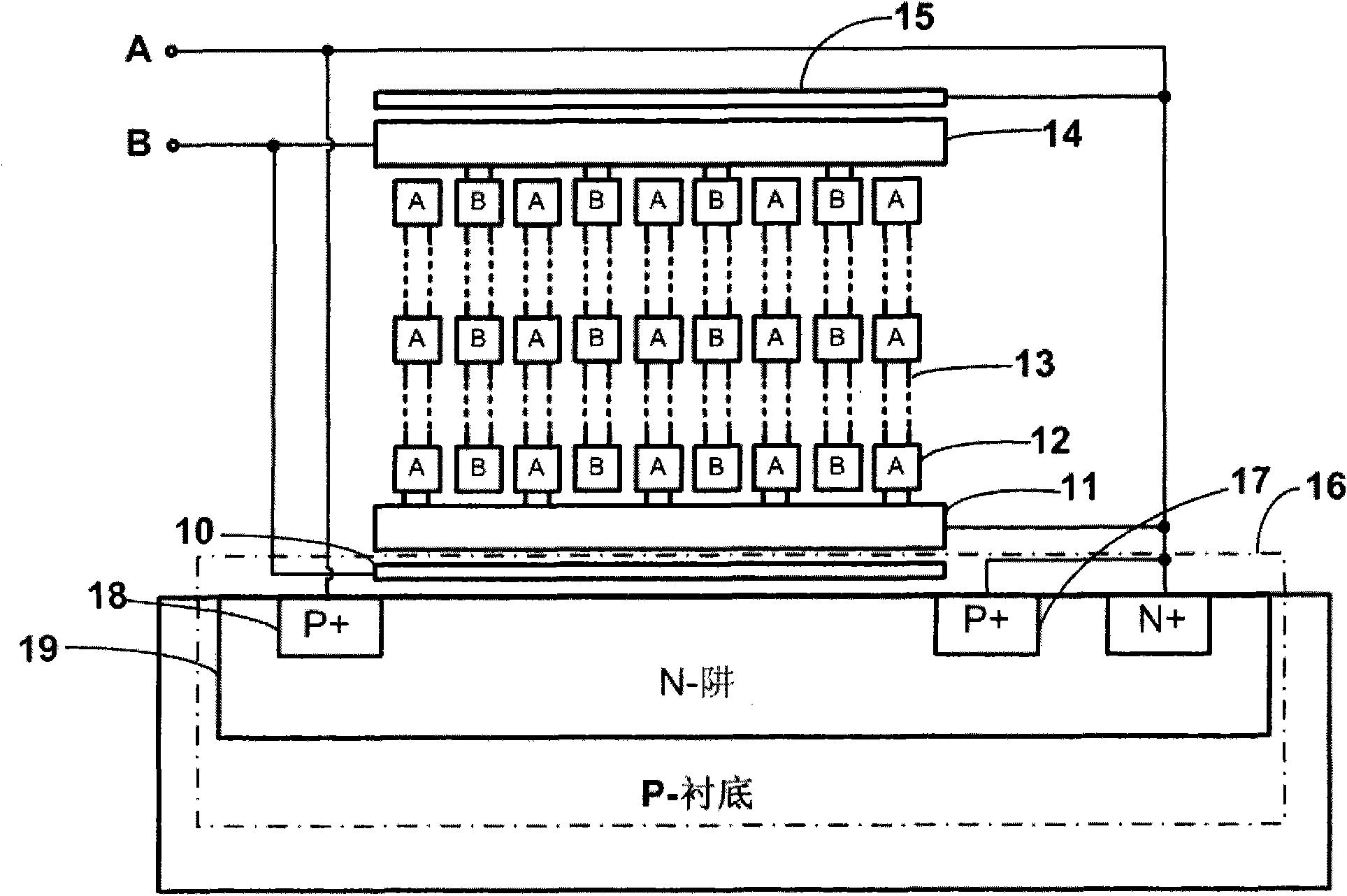

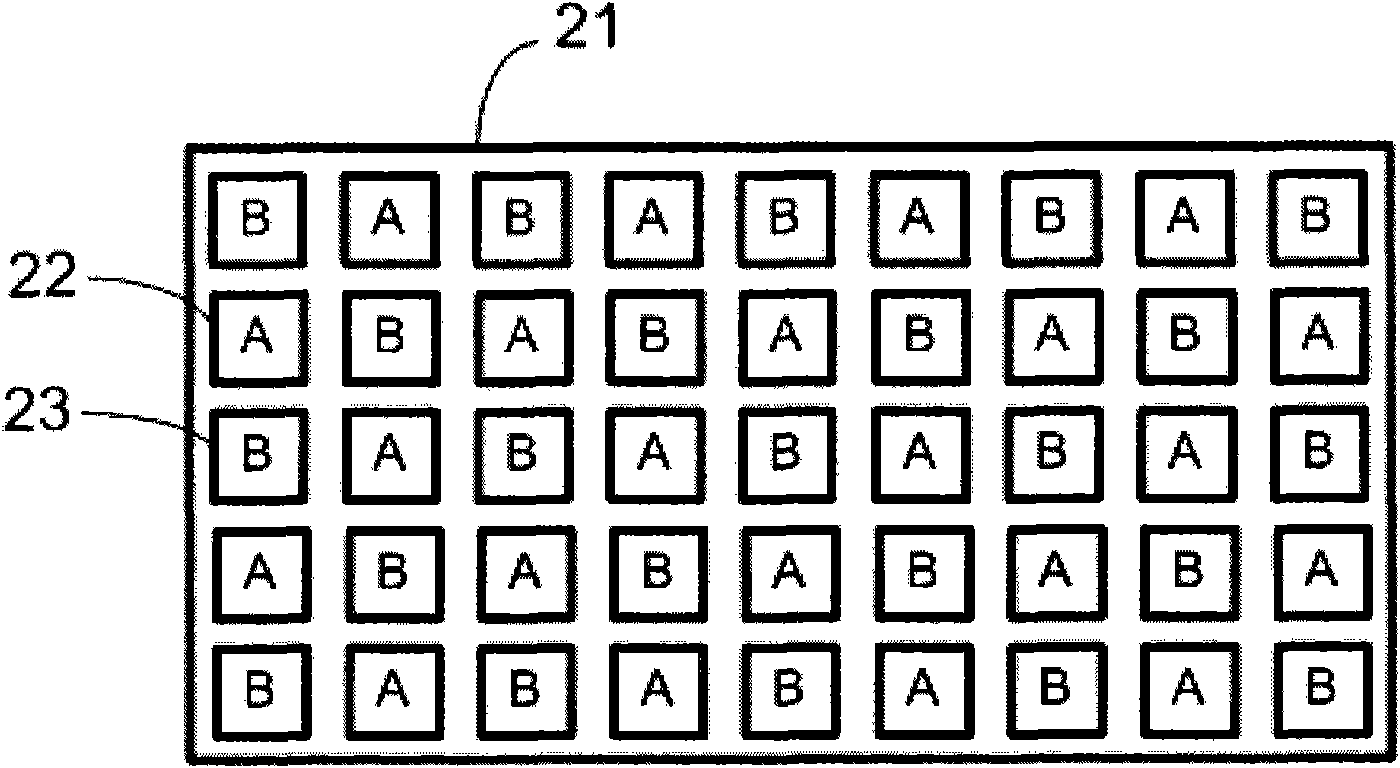

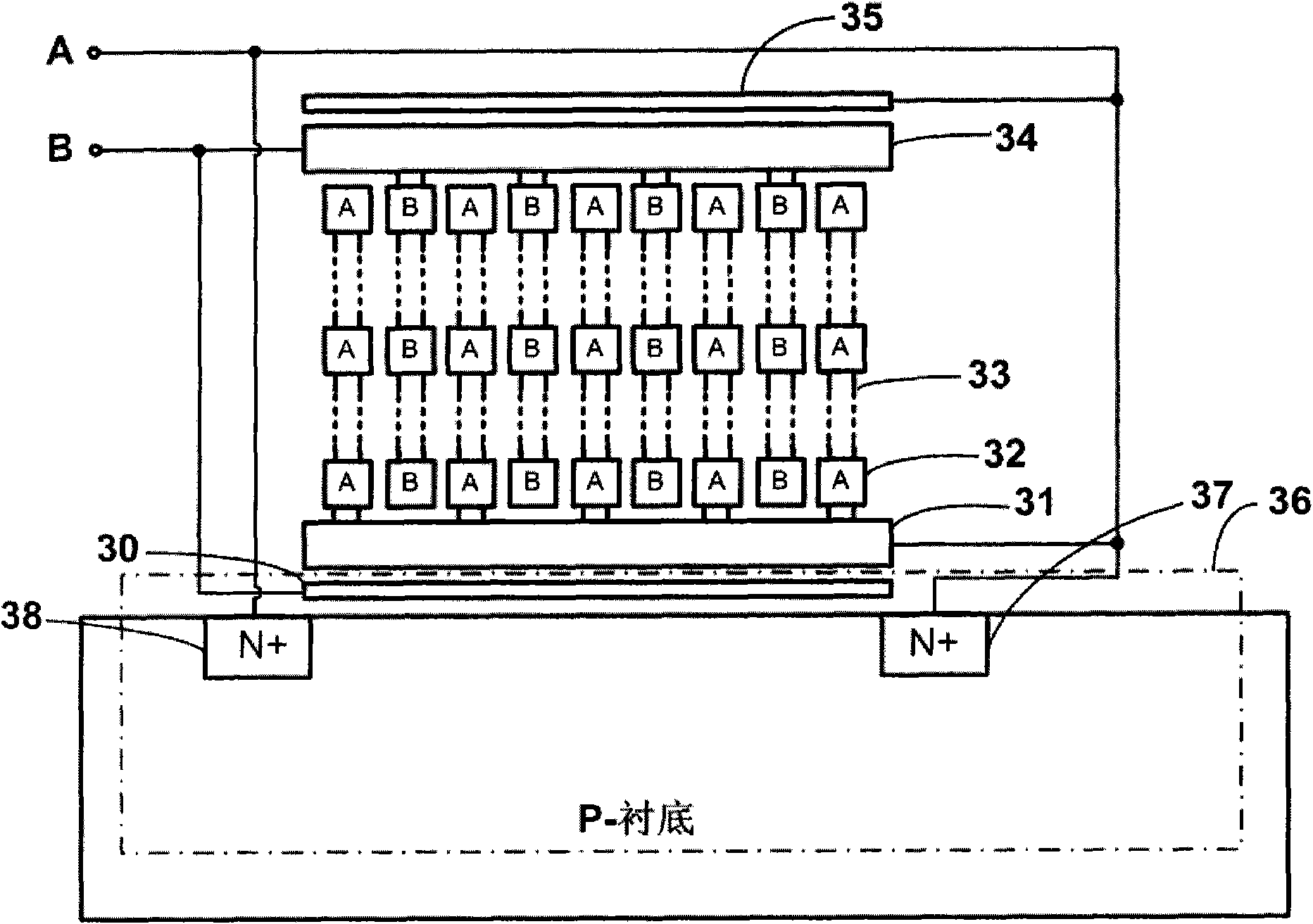

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0028] This high-density and low-parasitic capacitance device proposed by the present invention firstly realizes the maximization of capacitance per unit area, and secondly can effectively reduce the parasitic capacitance from the N well to the P substrate in the PMOS capacitance. In addition, the present invention adopts The special interlayer metal interconnection structure can maximize the capacitance between the same metal layers and the capacitance between via holes. With the decrease of process feature size, the improvement of lithography accuracy and the increase of metal layers, The distance between the metal layer and the metal layer, and the through hole can be further reduced, and the effective capacitance can b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com