Method for manufacturing integrated PNP differential pair tube

A manufacturing method and technology of differential pair tubes, which are applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of low reverse amplification factor, good symmetry of differential pair tubes, and high frequency, and reduce the saturation voltage drop. , the effect of high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

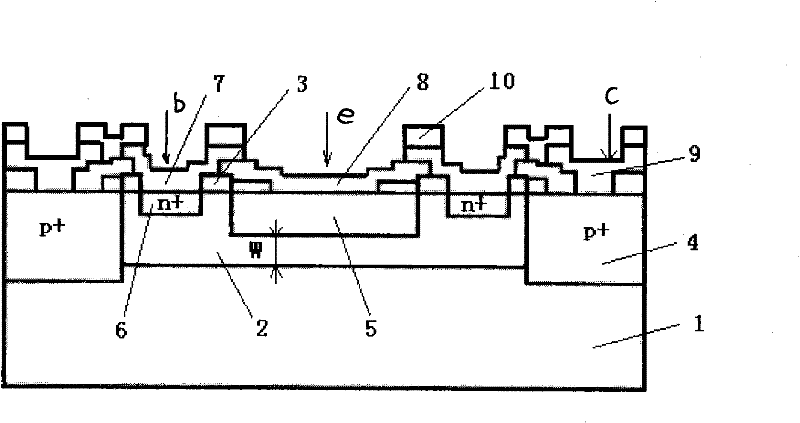

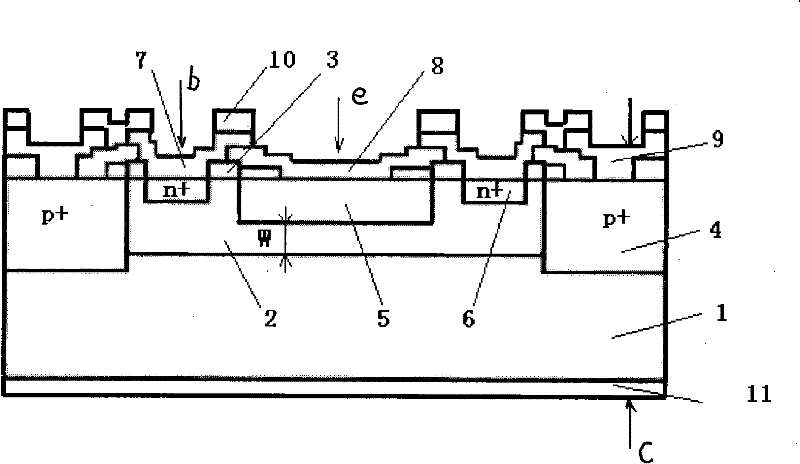

[0018] 1. If figure 1 with figure 2 As shown, the single-sided polished P+ silicon substrate 1 with crystal orientation has a resistivity of 0.001 ohm-cm, and an epitaxial layer is grown on the silicon substrate 1 as the N-base region 2, and the resistivity is 0.2 ohm-cm , with a thickness of 20 μm, an oxide layer 3 is grown by thermal oxidation;

[0019] 2. Diffusion of boron on the surface of the N base region 2 by photolithographic masking and etching, and the temperature of re-diffusion is 1160°C. The diffused boron junction is connected to the P+ silicon substrate 1 as the common P+ collector region 4 and forms a protective ring, and the epitaxial layer is separated into Two independent base regions, the surface impurity concentration of P+ collector region 4 is 10 20 / cm 3 ;

[0020] 3. Diffuse boron on the surface of the N-base region 2 to form a discrete emission region 5 through photolithographic masking and etching, and then diffuse at a temperature of 1000°C, ...

Embodiment 2

[0024] 1. If figure 1 with figure 2 As shown, the crystal direction is selected to polish the P+ silicon substrate 1 on one side, and its resistivity is 0.008 ohm-cm. An epitaxial layer is grown on the silicon substrate 1 as the N base region 2, and the resistivity is 2.0 ohm-cm. The thickness is 10 μm, and a layer of oxide layer 3 is grown by thermal oxidation;

[0025] 2. Diffusion of boron on the surface of the N base region 2 by photolithographic masking and etching, and the temperature of re-diffusion is 1200°C. The diffused boron junction is connected to the P+ silicon substrate 1 as the common P+ collector region 4 and forms a guard ring, and the epitaxial layer is separated into Two independent base regions, the surface impurity concentration of P+ collector region 4 is 4×10 19 / cm 3 ;

[0026] 3. Diffuse boron on the surface of the N-base region 3 to form the emitter region 5 by photolithographic masking and etching, and then diffuse at a temperature of 1160°C, ...

Embodiment 3

[0030] 1. If figure 1 with figure 2 As shown, the crystal direction is selected to polish the P+ silicon substrate 1 on one side, and its resistivity is 0.005 ohm-cm. An epitaxial layer is grown on the silicon substrate 1 as the N base region 2, and the resistivity is 1.0 ohm-cm. The thickness is 15 μm, and a layer of oxide layer 3 is grown by thermal oxidation;

[0031] 2. Diffuse boron on the surface of the N-base region 2 through photolithographic masking and etching, and the temperature of the re-diffusion is 1190°C. The diffused boron junction is connected to the P+ silicon substrate 1 as the common P+ collector region 4 and forms a guard ring, and the epitaxial layer is separated into Two independent base regions, the surface impurity concentration of P+ collector region 4 is 6×10 19 / cm 3 ;

[0032] 3. Diffuse boron on the surface of the N-base region 3 to form the emission region 5 by photolithographic masking and etching, and then diffuse at a temperature of 103...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com