Signal processing circuit

A signal processing circuit, input signal technology, applied in the direction of TV, color TV, electrical components, etc., can solve problems such as the inability to correctly express the amplitude of pulse-shaped signals, and achieve the effect of suppressing deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] (device structure)

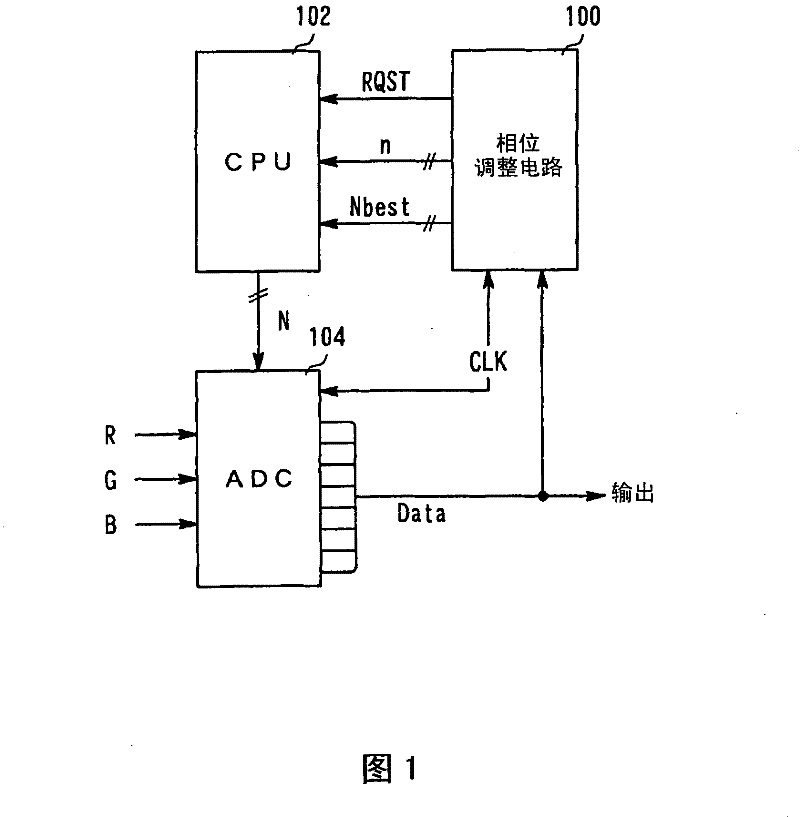

[0022] like figure 1 As shown, the signal processing circuit in the embodiment of the present invention includes a phase adjustment circuit 100 , a control unit (CPU) 102 and an analog / digital circuit (ADC) 104 . In this embodiment, a circuit for digitizing and sampling a video signal is described as an example of a signal processing circuit, but the signal processing circuit is not limited to this.

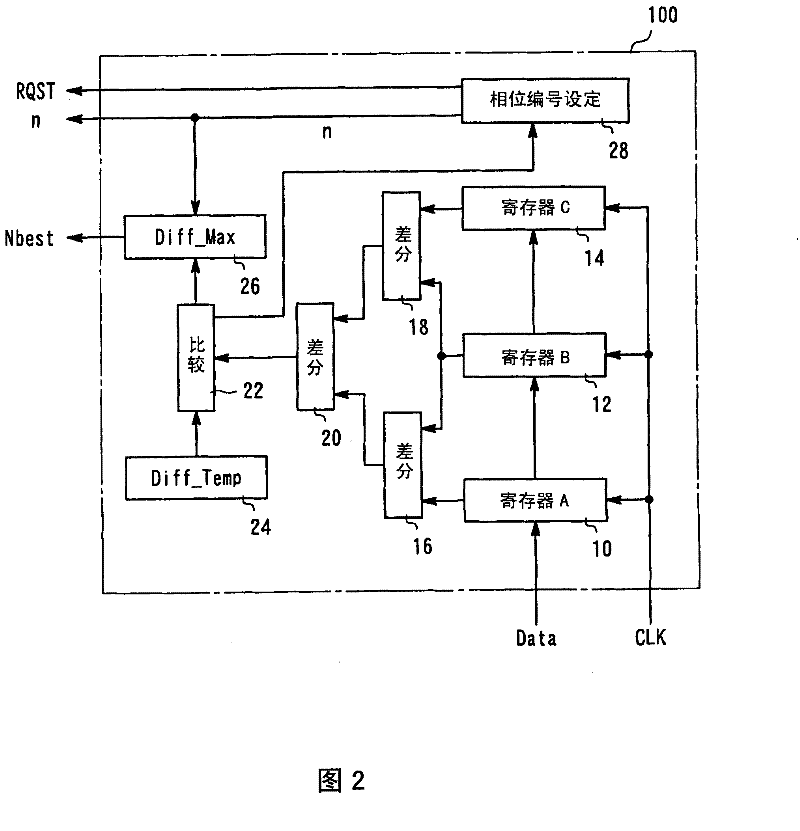

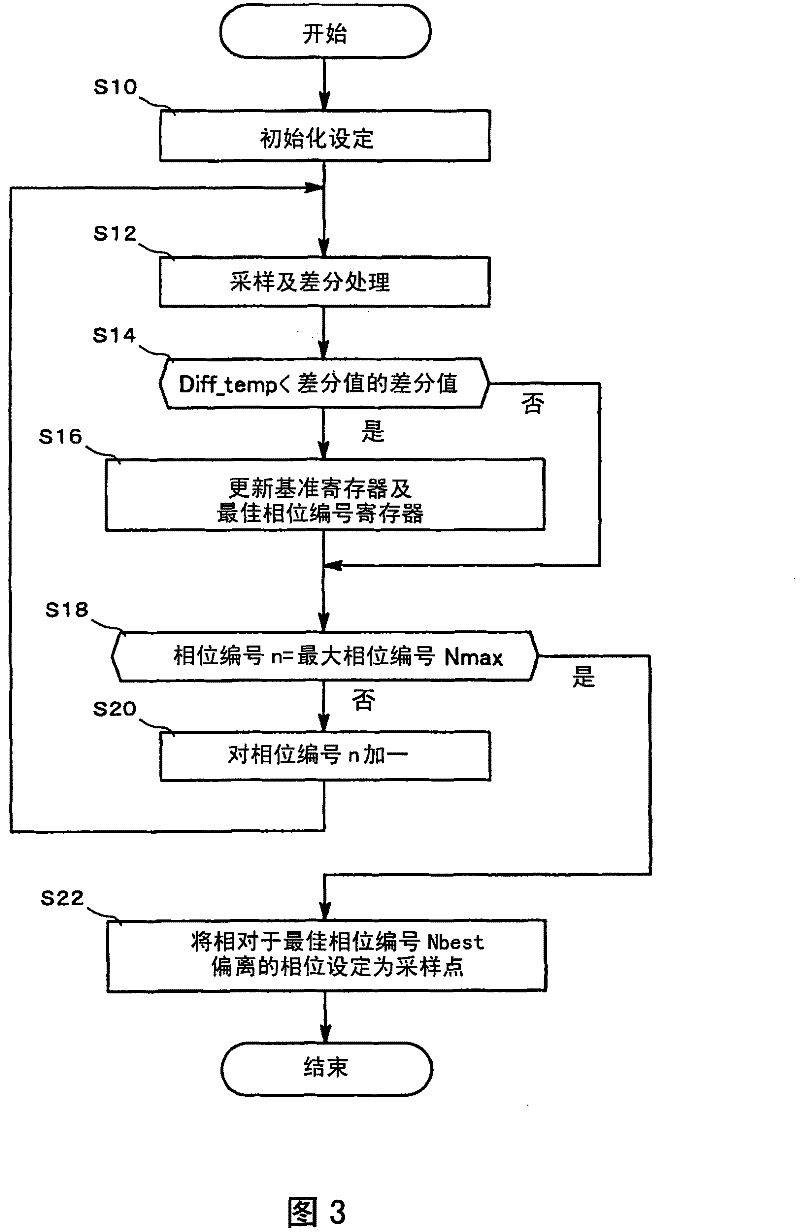

[0023] The phase adjustment circuit 100 receives the input signal Data and the reference clock CLK from the outside, generates a phase change request RQST, a phase number n, and a best phase number Nbest for matching the phases between the input signal Data and the reference clock CLK, and outputs them to CPU102. In order to sample the input signal Data and perform analog / digital conversion in the ADC 104, the phase change request RQST, the phase number n, and the optimum phase number Nbest are used. The operation of the phase adjustment circuit 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com