Method for preparing transistor T type nano grid

A transistor and nanotechnology, applied in the field of preparing high electron mobility transistor T-type nanogate, can solve the problems of increasing the alignment error of gate cap and gate foot, difficult to control fine line etching, difficult to remove electron beam glue, etc. Easy to remove glue, easy to control development time, easy to make effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

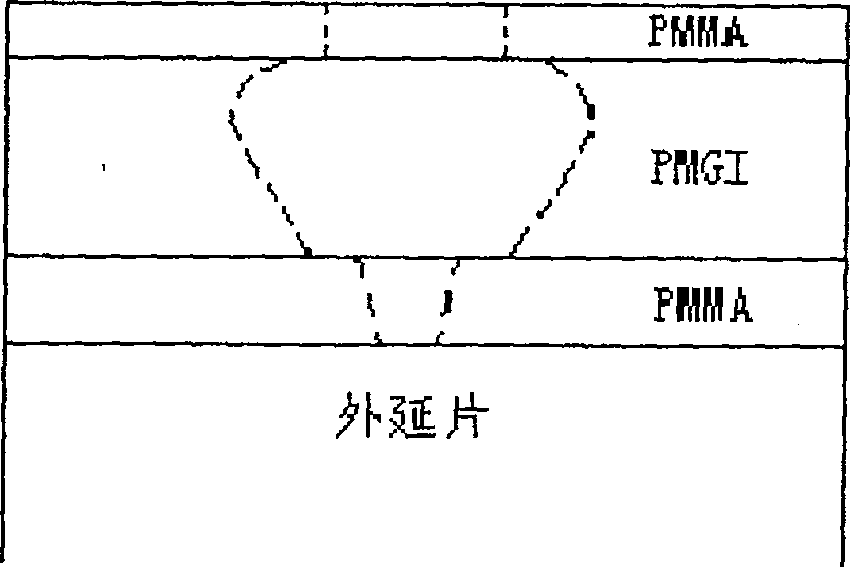

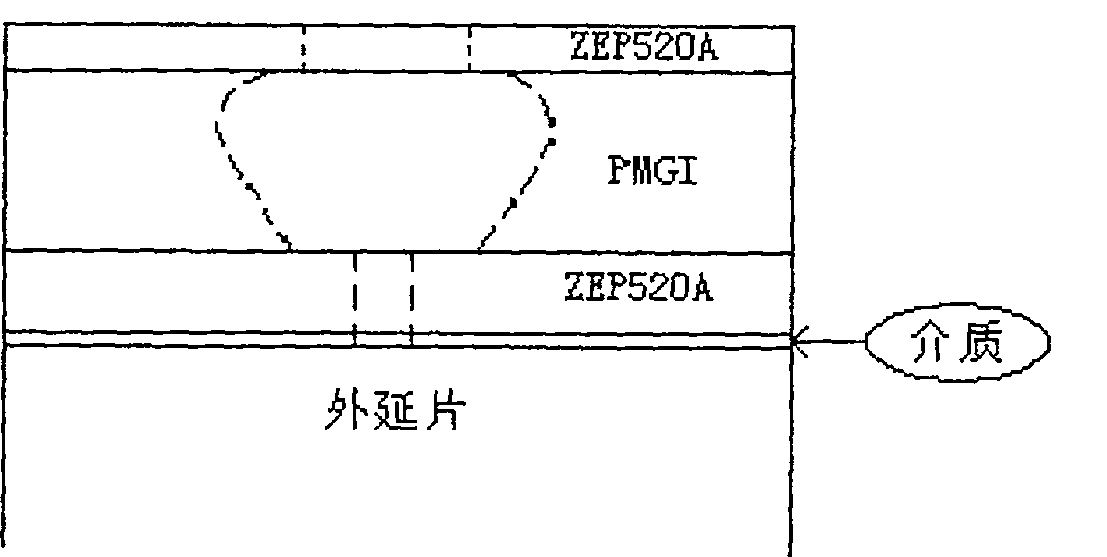

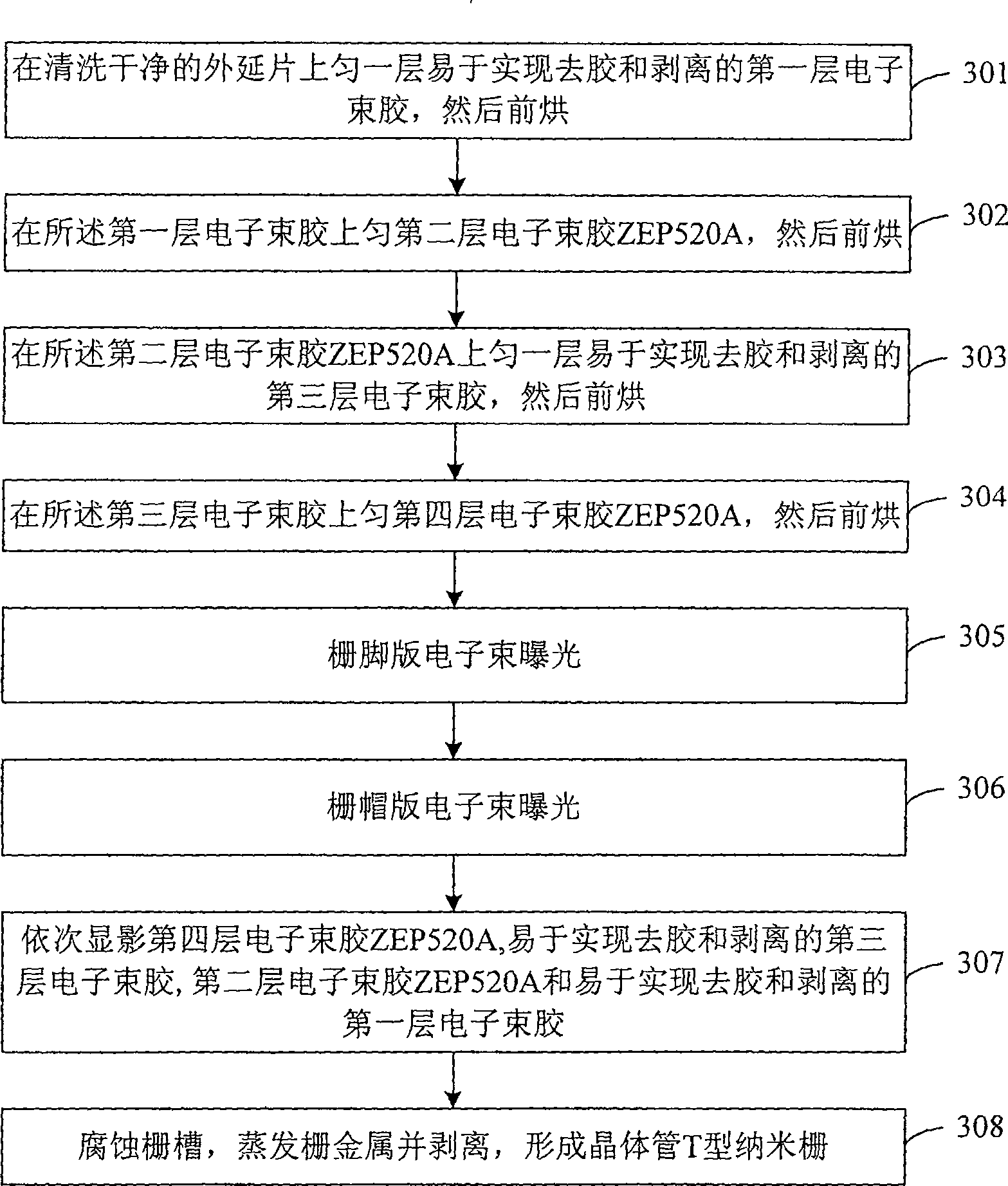

[0070] The method for preparing T-type nano-gates of high electron mobility transistors (HEMT) in this example is to address some shortcomings in the preparation of T-type nano-gates of high electron mobility transistors (HEMTs), using four layers of PMGI / ZEP520A / PMGI / ZEP520A Electron beam photoresist structure (as shown in Table 1) and two electron beam exposure methods to prepare high electron mobility transistor (HEMT) T-type nano-gate.

[0071] Table 1 is a structural representation of the PMGI / ZEP520A / PMGI / ZEP520A four-layer electron beam photoresist used in the method for preparing a high electron mobility transistor (HEMT) T-type nano-gate of the present invention:

[0072]

[0073] Table 1

[0074] In this embodiment, the first layer of electron beam glue and the third layer of electron beam glue that are easy to realize deglue and stripping are PMGI electron beam glue, which is used in the preparation method of high electron mobility transistor (HEMT) T-type nano-g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com