Silicon extension of re-doped arsenic substrate

A technology of silicon epitaxy and substrate, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of high resistance layer of epitaxial layer, affecting impurity content, and the amount of impurity diffusing outward, reaching the transition zone Effects of flatness, suppression of self-doping, and uniform resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Below in conjunction with concrete experimental result the present invention is described in further detail:

[0035] In this embodiment, the conventional "two-step epitaxy method" and the method of the present invention were used to test respectively, and the test data were compared.

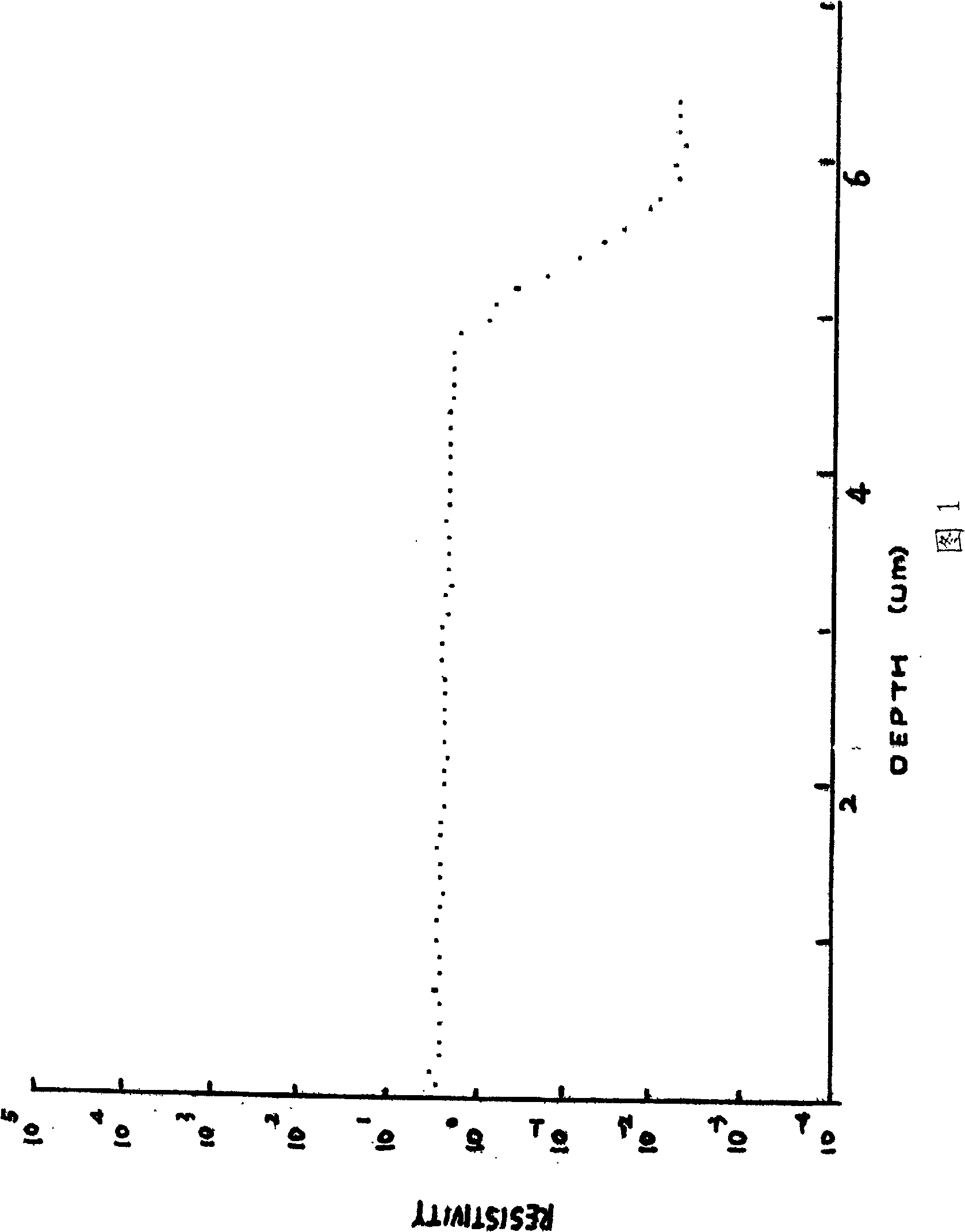

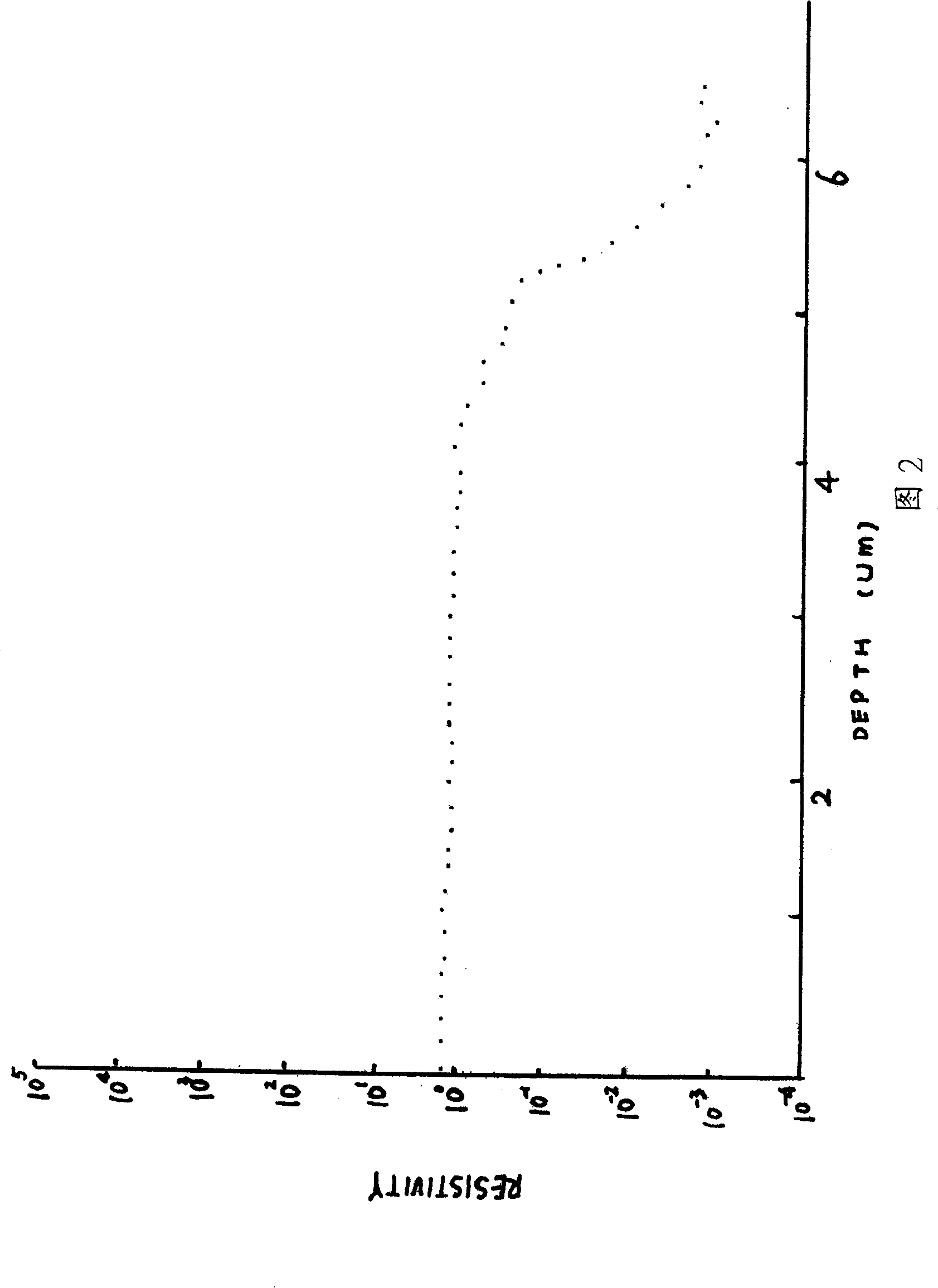

[0036] The epitaxial parameters of the epitaxial layer in this embodiment are: the resistivity of the epitaxial layer is 0.70-0.78Ω·cm, and the thickness of the epitaxial layer is 4.9-5.2um.

[0037] The epitaxial equipment adopted in this embodiment is: PE2061 epitaxial furnace of Italy LPE Company, each furnace can hold 30 four-inch silicon wafers.

[0038] The specific process steps in this embodiment are as follows: Furnace installation-heating to 1000-1200°C-introduction of HCl into the furnace for polishing-use of large flow of H 2 Rinse--grow a layer of intrinsic epitaxial layer with a thickness of about 1.5um--again use large flow H 2 Rinse while passing H 2 Introduce 1% HCl—t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com