Method for encapsulating crystal circular piled multi-chips

A packaging method and multi-chip technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing the difficulty of the process, complicated and time-consuming, chip fragmentation, etc., to improve the fragmentation problem, increase memory capacitance, and improve process efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0022] Please refer to Figure 7a , provide a first wafer 700 with a chip array, this chip array is composed of a number of first chips 702 that have not been separated, and the chip back 703 of the first wafer 700 is adhered and fixed on the first plastic frame with an adhesive tape 704 706 (film frame). The chips 702 are precut from the chip active surface 707 of the wafer 700 to a depth to define first chips 702 equidistant from each other, wherein the cut depth is less than the thickness of the wafer 700 .

[0023] Please refer to Figure 7b A second glue frame 708 is adhered on the chip active surface 707 of these pre-cut first chips 702, so as to facilitate subsequent fixing of the completely cut first chips 702. Please refer to Figure 7c , using the second glue frame 708 to turn the first wafer over so that the chip backside 703 faces upward, and remove the first glue frame 706 . Please refer to Figure 7d The wafer 700 is thinned to a certain thickness from the c...

no. 2 example

[0029] Please refer to Figure 8a , providing a first wafer 800 with a chip array (not shown), wherein the chip array is composed of a plurality of unseparated first chips.

[0030] Please refer to Figure 8b Thinning the wafer 800 from the chip back side 803 of the wafer 800, and adhering and fixing the chip back side 803 of the first wafer 800 on the first plastic frame 806 (film frame) with adhesive tape 804, so as to facilitate subsequent fixing and separate separation chips, where the thinning method cannot be limited to chemical mechanical polishing or general mechanical polishing.

[0031] Please refer to Figure 8c, by cutting the first chip 802 on the active surface 807 of the chip, the first chips 802 arranged equidistantly from each other are defined, wherein the cutting depth is smaller than the thickness of the wafer 800, and the first wafer is turned over by the second glue frame 808 Make the back side of the chip 803 face up, and remove the first plastic fram...

no. 3 example

[0033] Please refer to Figure 9a , provide a chip array, which includes a plurality of independent first chips 902 on a plastic frame 906, the first chips 902 are cut from the first wafer, wherein the manufacturing steps can directly refer to the above-mentioned second embodiment related steps.

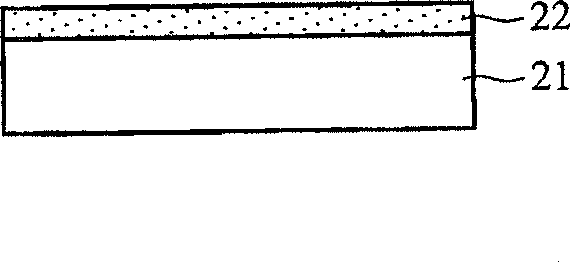

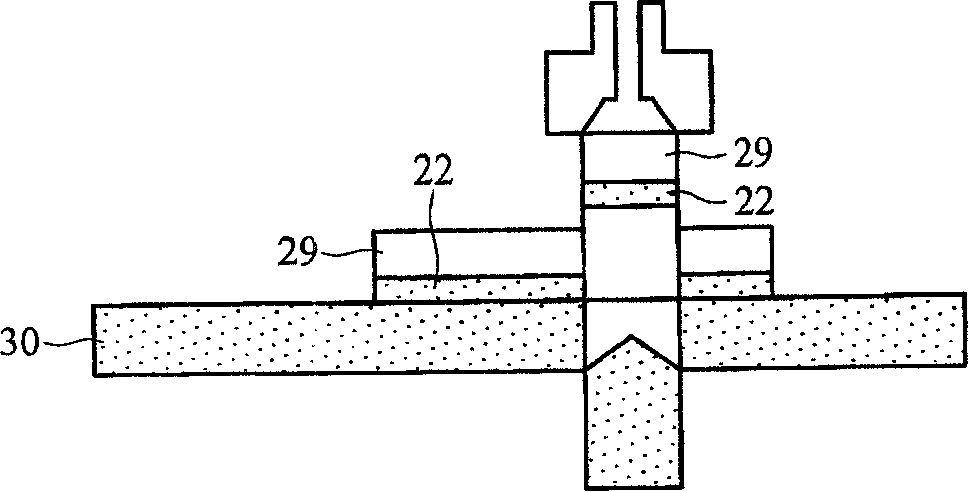

[0034] Please refer to Figure 9b , provide a thinned second wafer 910 , which has a plurality of chips (not shown) arranged equidistantly, and form an adhesive layer 912 on the chip active surface 914 of the second wafer 910 . Wherein the adhesive layer 912 is fully formed on the second wafer 910 or selectively formed on the part of the second wafer 910 overlapping with the first chip 902, and its material can be epoxy resin, thermoplastic or B -stage glue, formed as a paste or pre-formed film, which can deposit a paste material using automated paste dispensing equipment, or if the adhesive layer 912 material is a pre-formed material, can be directly attached to the chip backside ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com