Adaptive mode switching of flash memory address mapping based on host usage characteristics

a flash memory and host usage characteristic technology, applied in the direction of memory address formation, memory allocation/allocation/relocation, instruments, etc., can solve the problems of shortening the useful life of the data consolidation operation, affecting the performance, etc., to achieve optimal performance characteristics, shorten the useful life, and improve performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

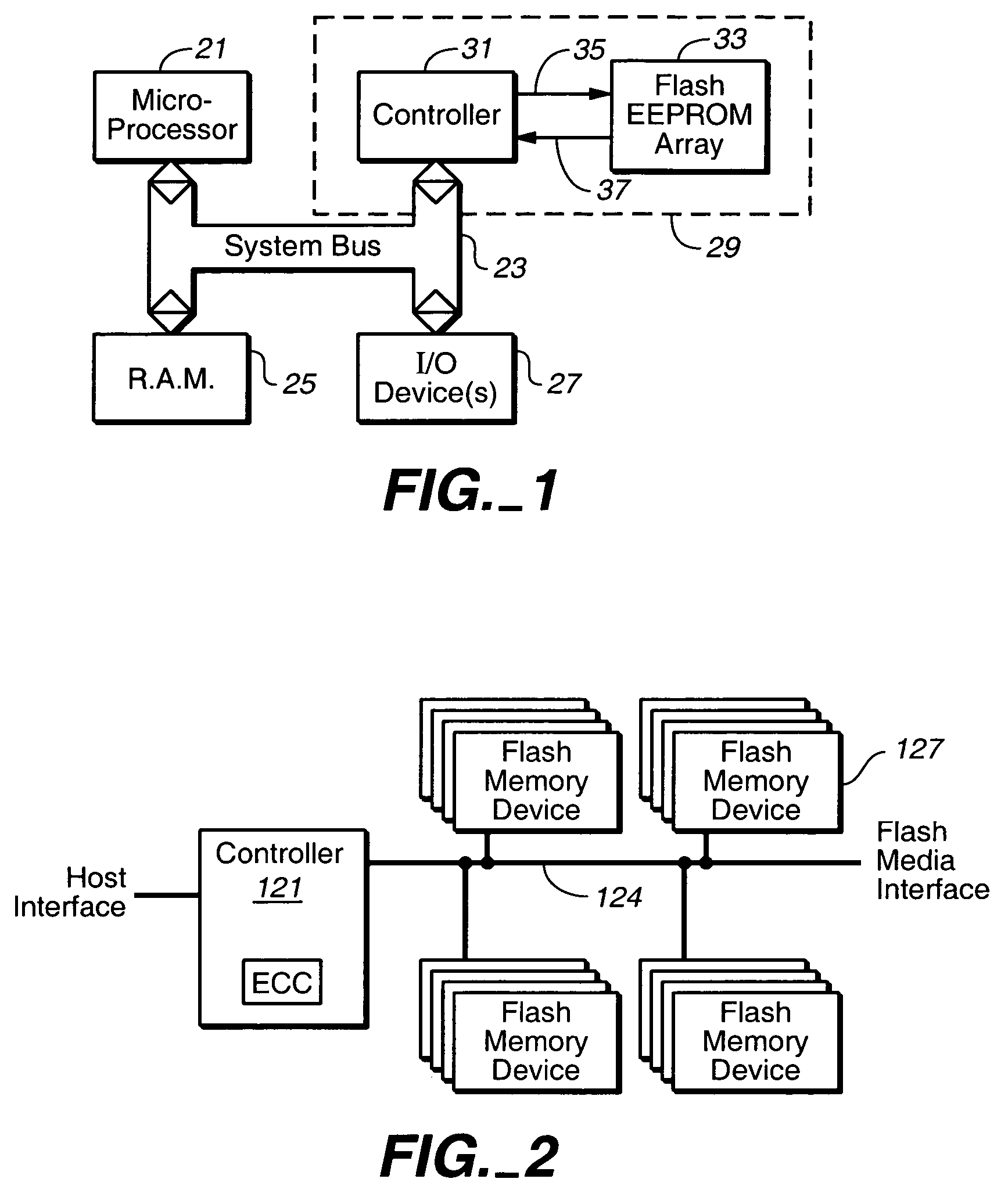

[0032]FIG. 1 generally shows an electronic system, such as a computer system, that includes a flash memory system in which various aspects of the present invention may be incorporated. Some examples of this electronic system include desktop computers, laptop computers, handheld computers, palmtop computers, personal digital assistants (PDAs), MP3 and other audio players, digital cameras, video cameras, electronic game machines, wireless and wired telephony devices, answering machines, voice recorders, network routers and others.

[0033]This electronic system of FIG. 1 includes a processor or microprocessor 21 connected to a system bus 23, along with random access, main system memory 25, and at least one or more input-output devices 27, such as a keyboard, monitor, modem, and the like. Another main computer system component that is connected to a typical computer system bus 23 is an amount of long-term, non-volatile memory. In contrast to volatile memory such as DRAM (dynamic RAM) or S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com