Method and structure to enhance gate induced strain effect in multigate device

a multi-gate device and gate induced strain technology, applied in the field of semiconductor device manufacturing, can solve the problems of increasing the difficulty of meeting the transistor drive current performance, significantly reducing the stressor volume, so as to increase the mobility and drive current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

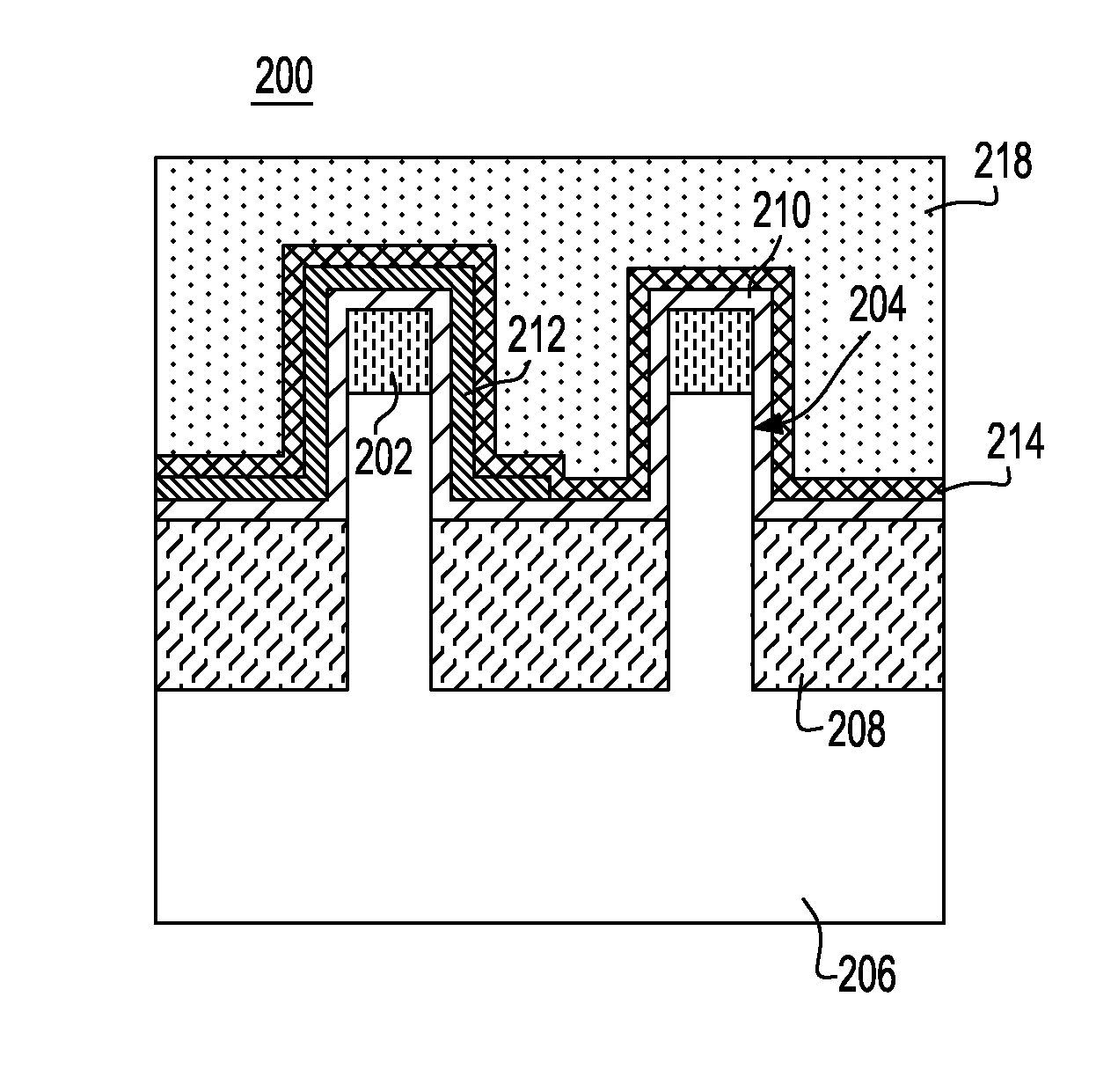

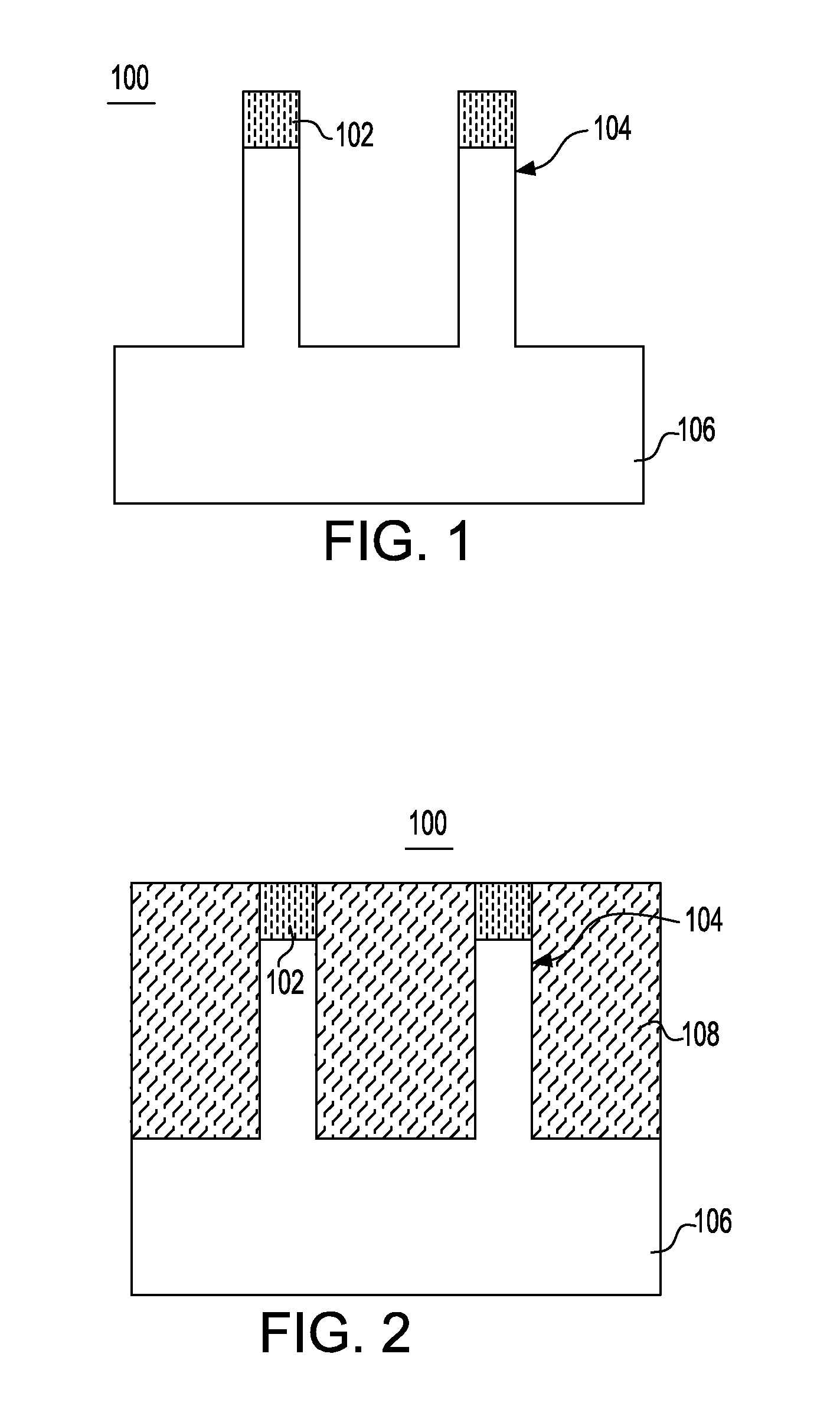

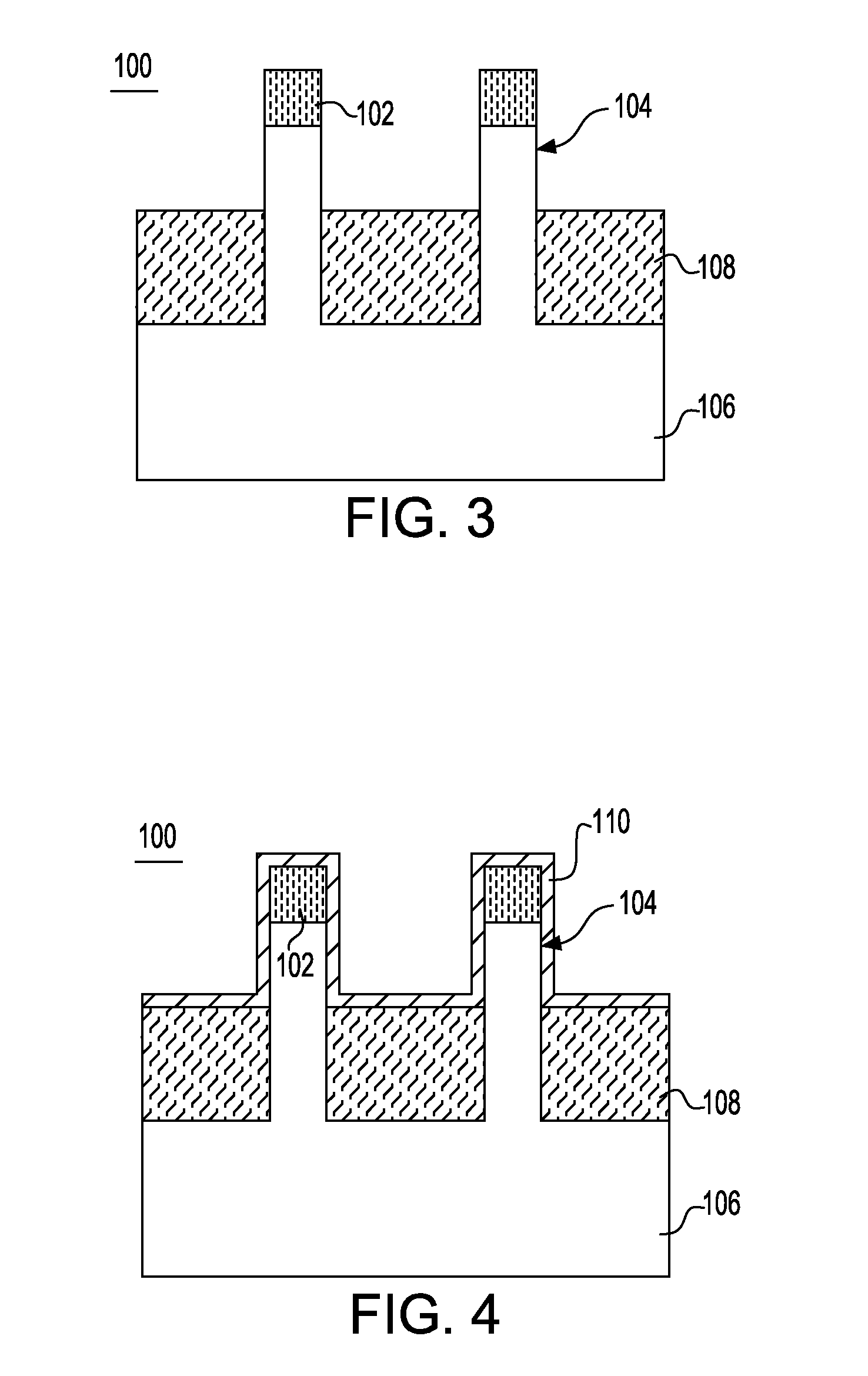

[0030]It will be appreciated that for simplicity and clarity of illustration, elements shown in the drawings are not necessarily drawn to scale. For example, the dimensions of some of the elements may be exaggerated relative to other elements for clarity. As previously stated, the present disclosure relates to a semiconductor structure including locally thinned semiconductor fins, and a method for manufacturing the same. Aspects of the present disclosure will now be described in detail with accompanying figures. It is noted that like reference numerals refer to like elements across different embodiments. As used herein, ordinals such as “first” and “second” are employed merely to distinguish similar elements, and different ordinals may be employed to designate a same element in the specification and / or claims.

[0031]In a first exemplary semiconductor structure according to a first embodiment of the present disclosure can be formed by providing a semiconductor substrate, which can be ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com