Semiconductor device having data bus

a data bus and semiconductor technology, applied in semiconductor devices, digital storage, instruments, etc., can solve the problems of difficult design in such a manner, difficult to sufficiently suppress the coupling capacitance cc, and deterioration of transmission quality, so as to suppress the influence of crosstalk of the data bus, and reduce the coupling capacitan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]Preferred embodiments will be described in detail below with reference to accompanying drawings. The following embodiments disclose a DRAM (Dynamic Random Access Memory) as an example of the semiconductor device.

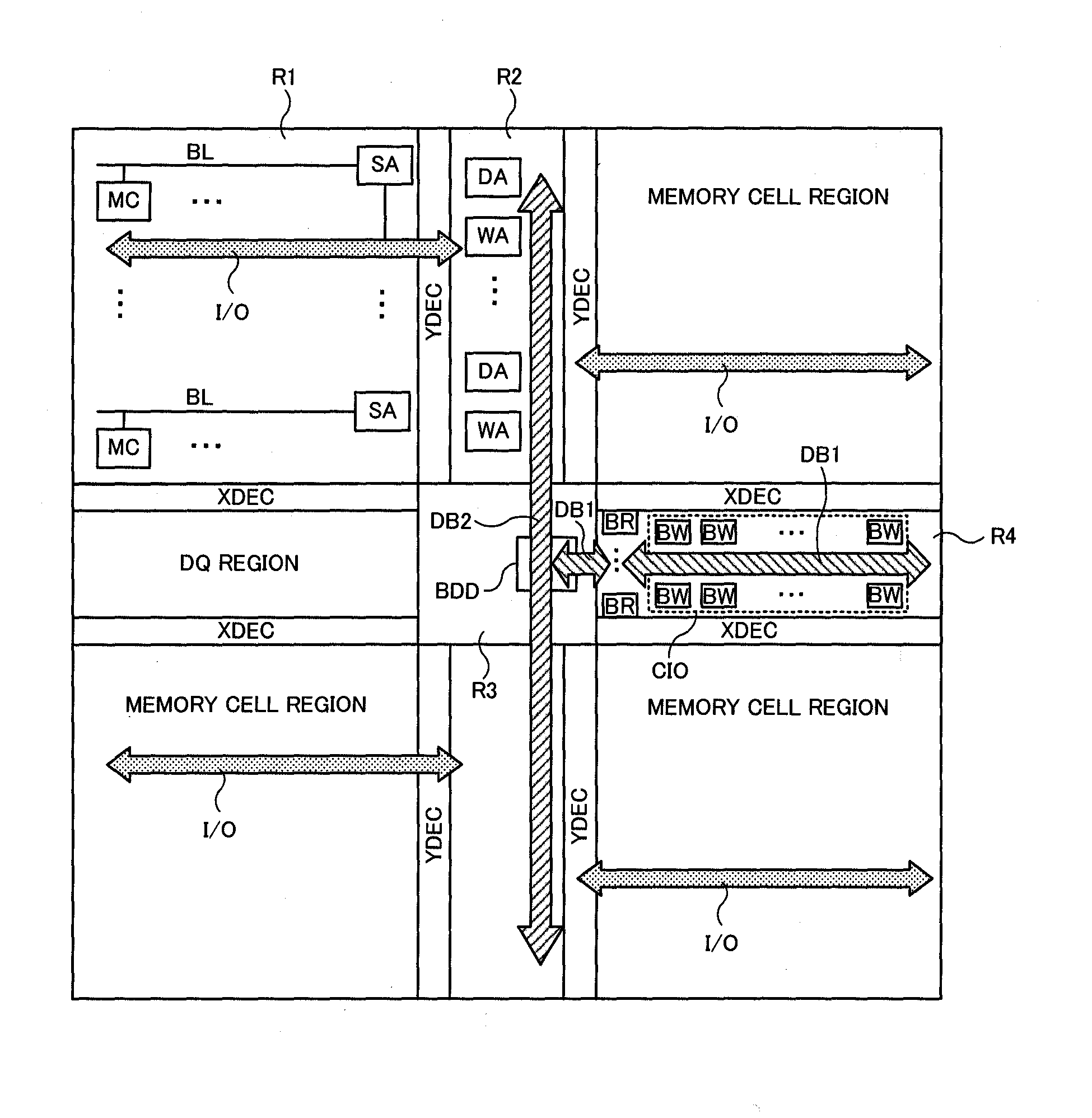

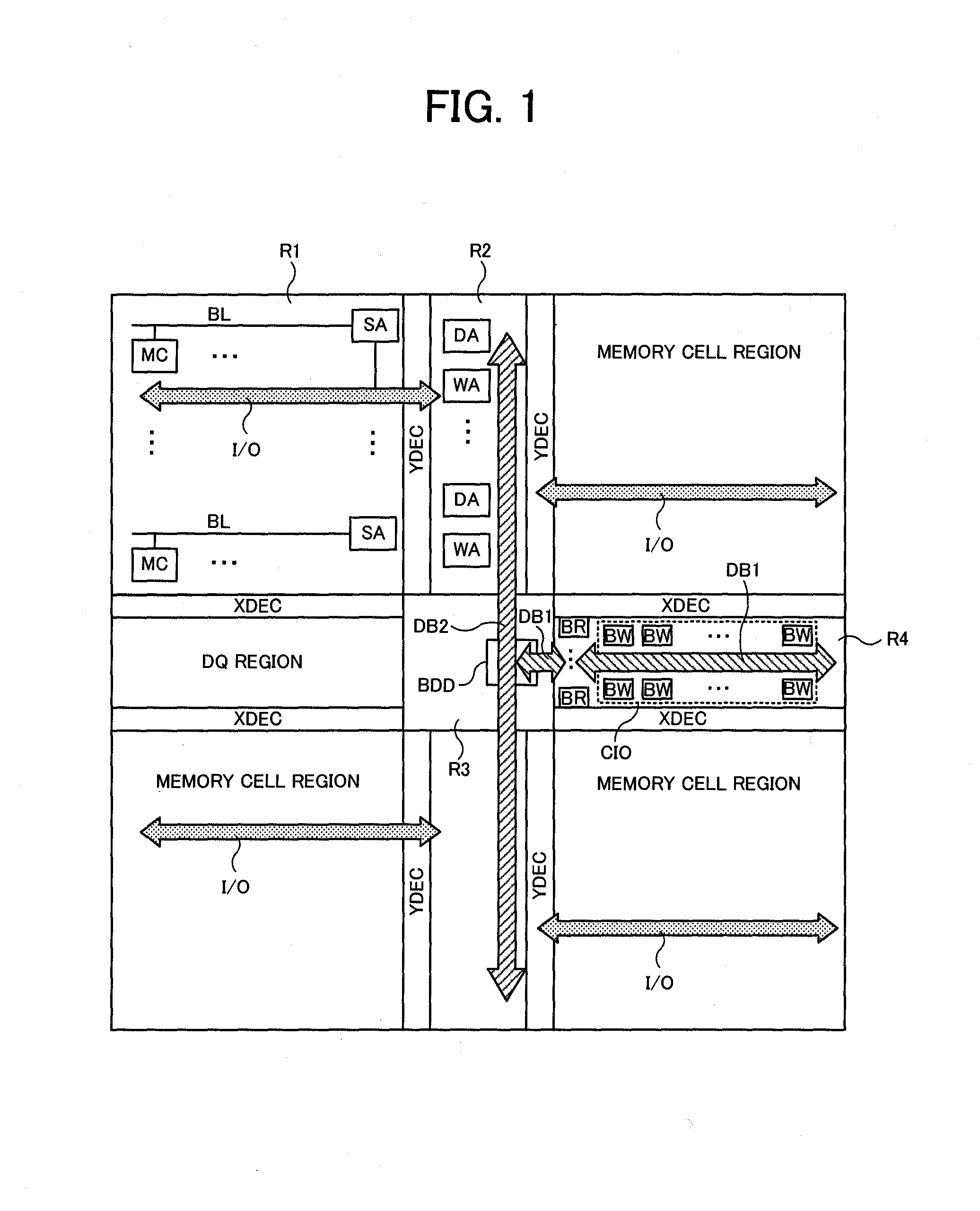

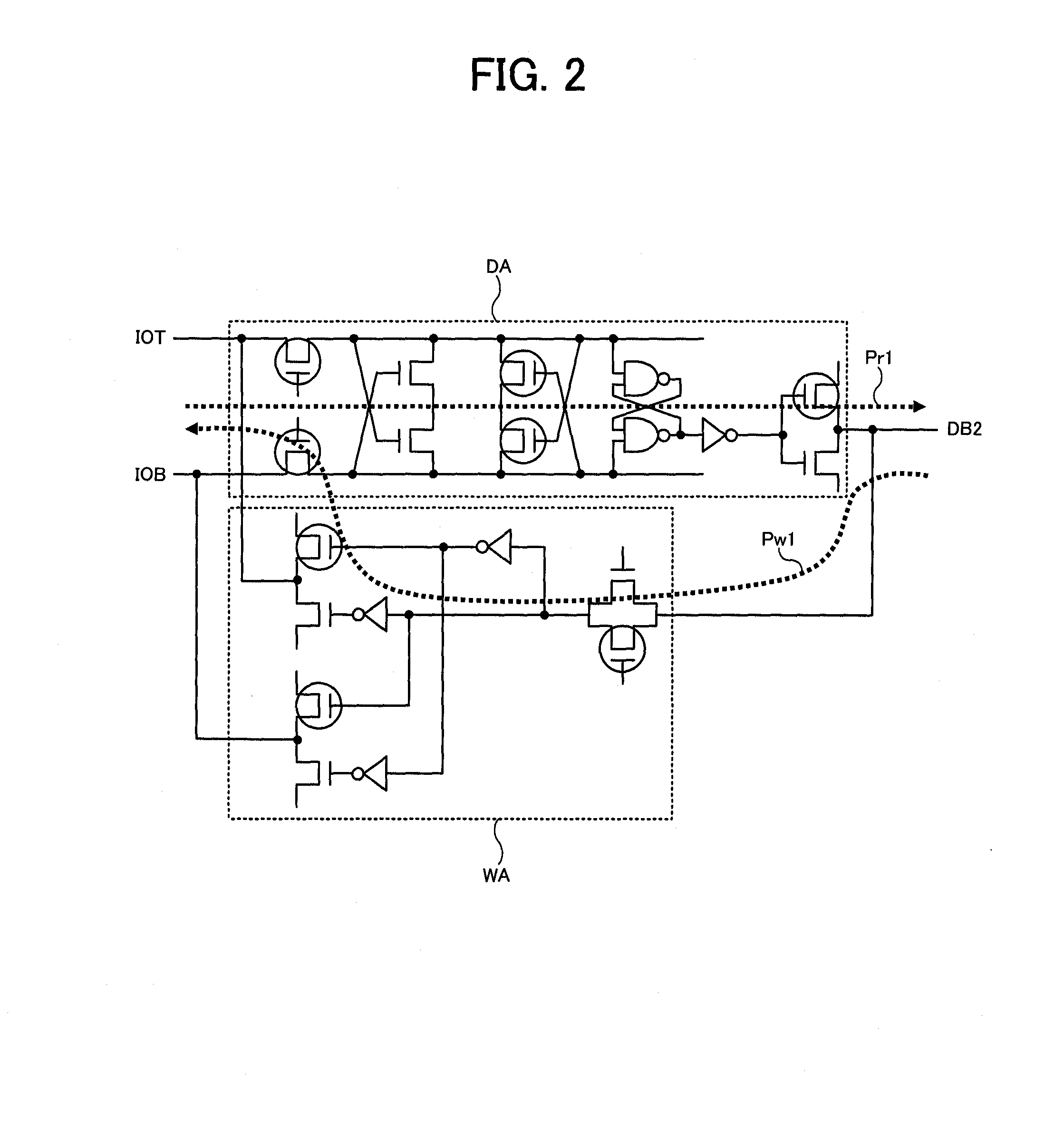

[0033]FIG. 1 is a block diagram showing an entire configuration of the DRAM of the embodiments. The DRAM shown in FIG. 1 is partitioned into a memory cell region R1, an amplifier region R2, a center region R3, and a DQ region R4. In the memory cell region R1, there are provided a plurality of memory cells MC arranged at intersections of a plurality of word lines (not shown) and a plurality of bit lines BL, a plurality of sense amplifiers SA connected to one ends of the bit lines BL, and a plurality of input / output lines I / O selectively connected to the sense amplifiers SA. In addition, an X decoder XDEC arranged at an end in a word line extending direction and a Y decoder YDEC arranged at an end in a bit line extending direction are attached to the memory cell region R...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com