Semiconductor memory device

A storage device and semiconductor technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of high power consumption, slow action speed, etc., to suppress the influence of crosstalk, expand the interval between wiring, reduce Effect of inter-wiring capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, the semiconductor memory device of the present invention will be described in detail with reference to the drawings.

[0027] First, the memory cell of the semiconductor memory device of the present invention will be described.

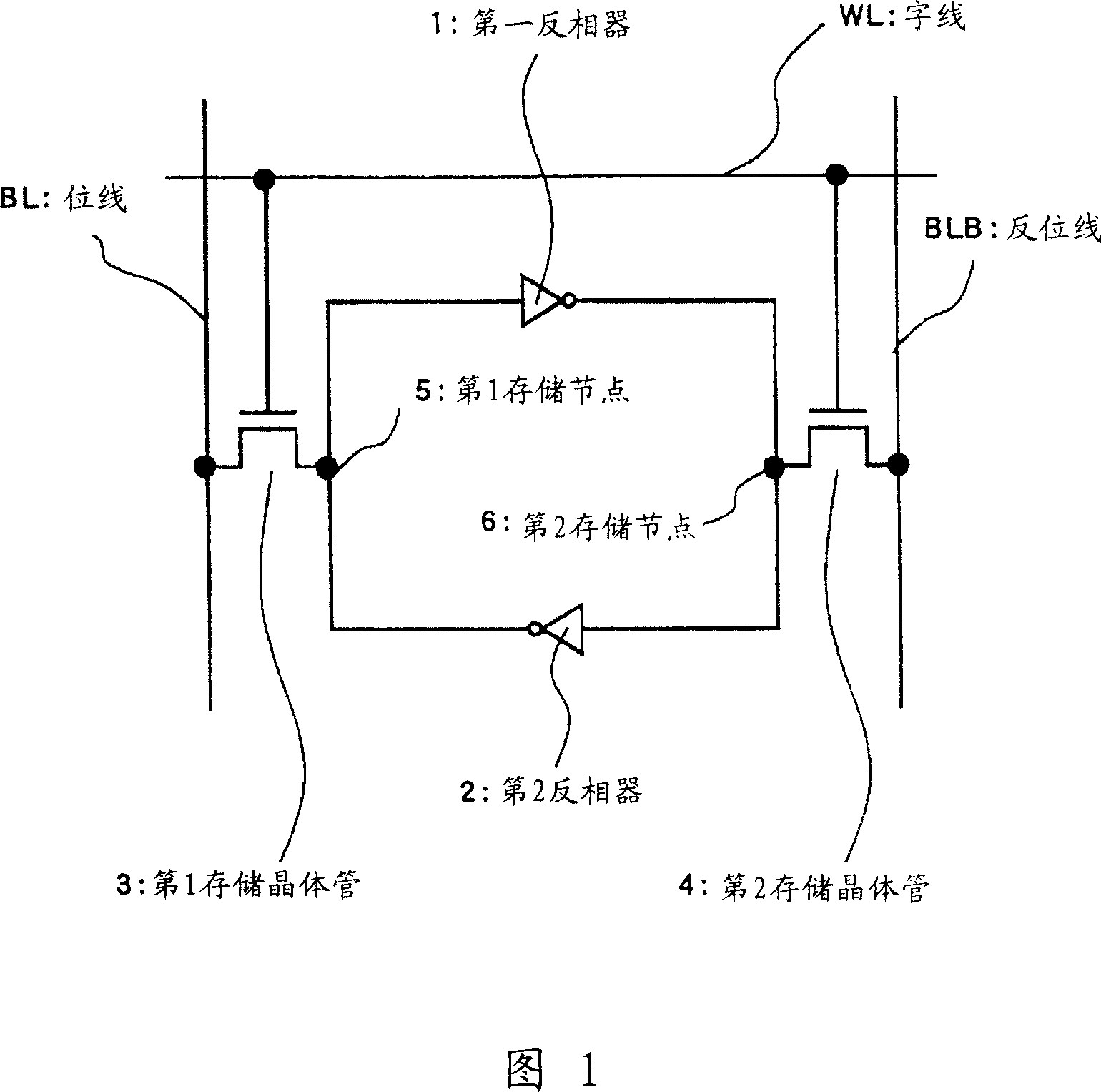

[0028] FIG. 1 is a diagram showing an SRAM used as a memory cell.

[0029] The first inverter 1 and the second inverter 2 constitute a latch circuit in which inputs and outputs are cross-connected. Furthermore, the gates of the first access transistor 3 and the second access transistor 4 are commonly connected to the word line WL. Next, the first access transistor 3 and the second access transistor 4 are respectively connected to the first storage node 5 and the second storage node 6 , the bit line BL and the reverse bit line BLB.

[0030] The above SRAM operates as follows. That is, first, the bit line BL and the reverse bit line BLB are applied with an H potential to be in a precharged state. Next, in the precharge state, H p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com