Semiconductor device and method of manufacturing the semiconductor device

a semiconductor and semiconductor technology, applied in the direction of semiconductor devices, electrical appliances, transistors, etc., can solve the problems of difficult to establish a low-resistance contact between silicon and minority bits, impaired transistor uniformity, and limited minority bits in the dram, so as to achieve the effect of limiting the thickness of the gate oxide film and ensuring the uniformity of transistor characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]The invention will be now described herein with reference to an illustrative embodiment. Those skilled in the art will recognize that many alternative embodiments can be accomplished using the teachings of the present invention and that the invention is not limited to the embodiment illustrated for explanatory purposes.

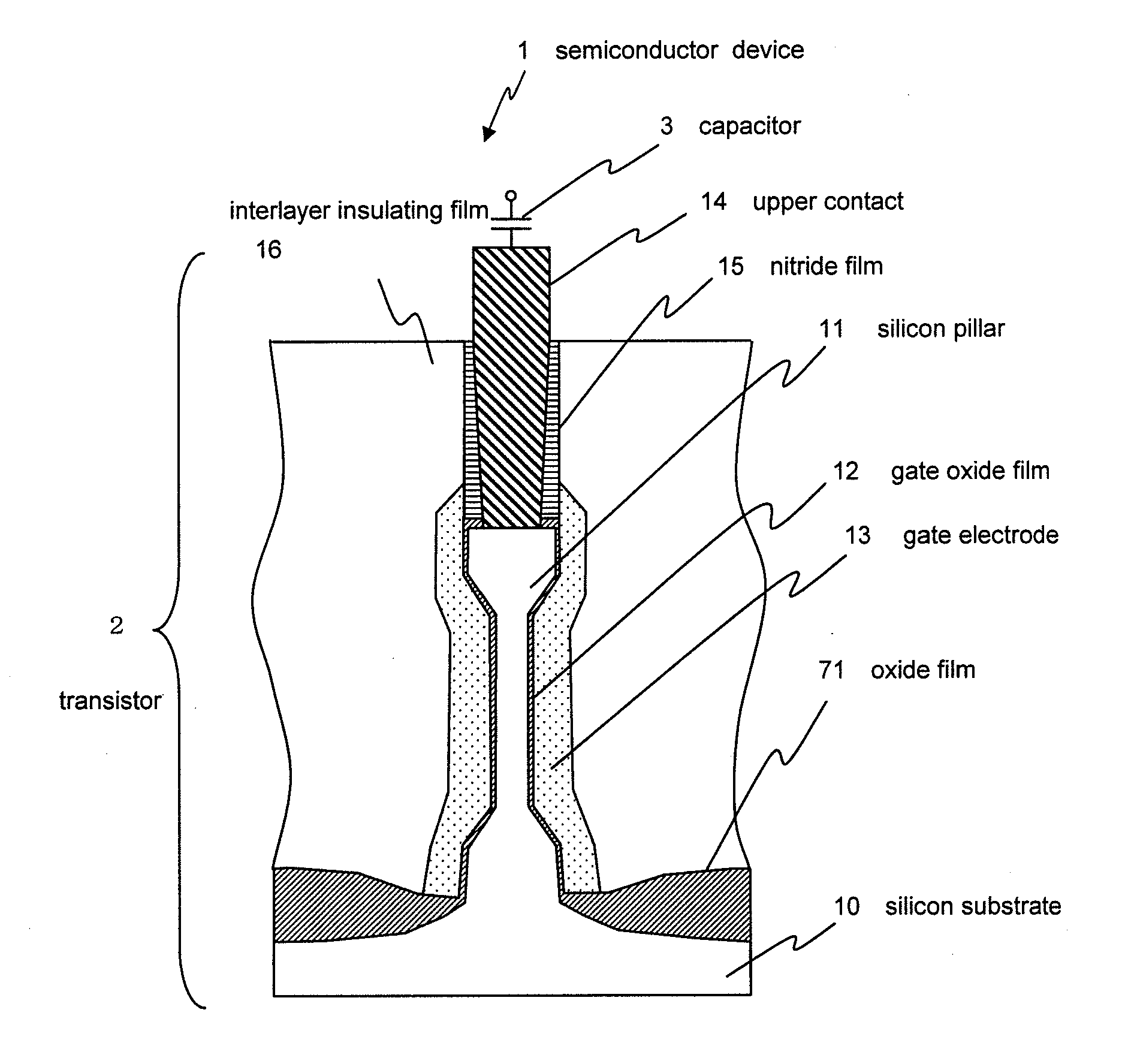

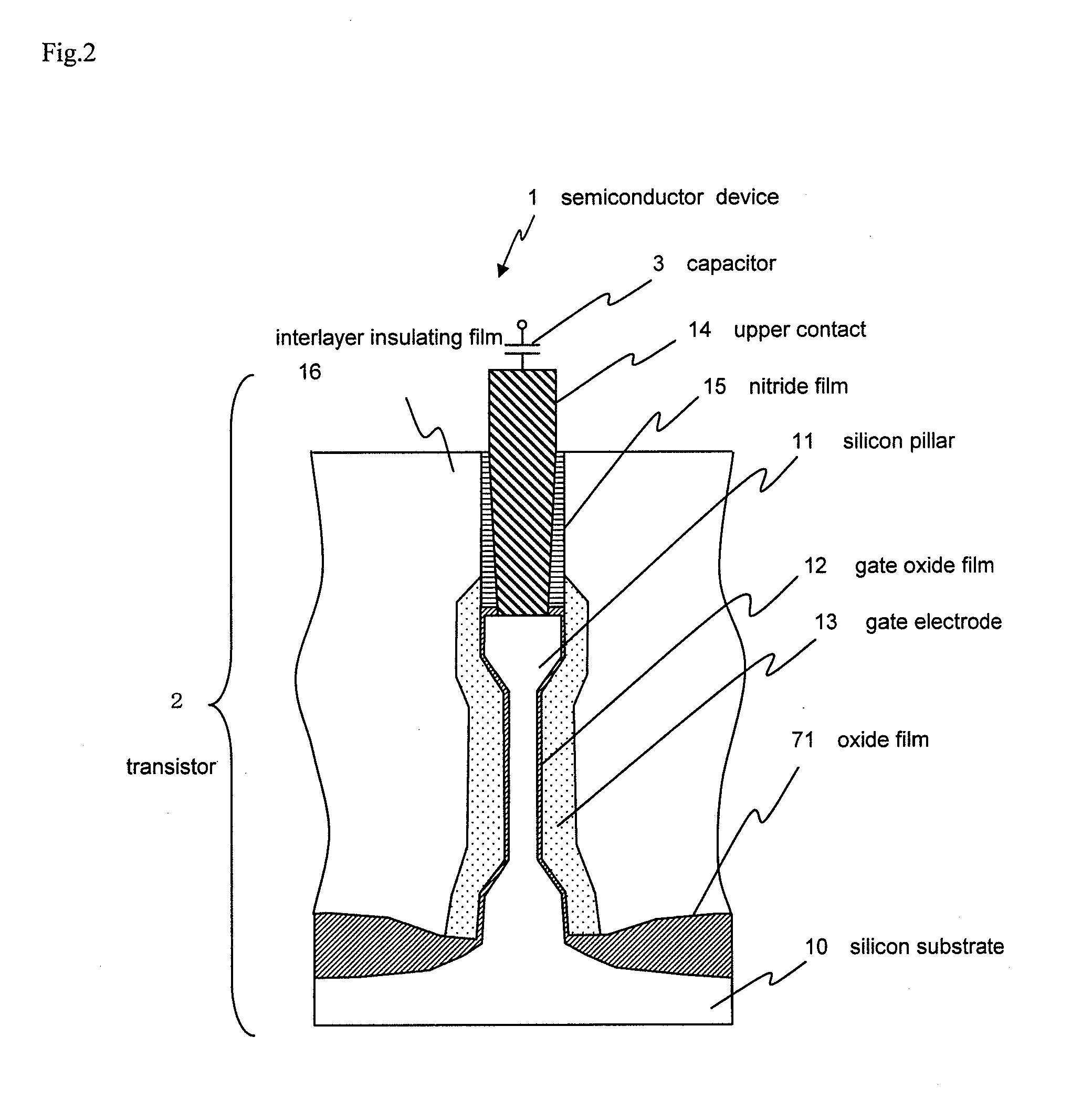

[0031]A semiconductor device in a first embodiment is a semiconductor memory which includes a capacitor and a transistor which are disposed and which are in a superposed condition and connected to each other in series. FIG. 2 is a sectional view showing the structure of a main portion of the semiconductor device in the exemplary embodiment.

[0032]Semiconductor device 1 of the exemplary embodiment has, as shown in FIG. 2, transistor 2 and capacitor 3 disposed by being superposed on transistor 2 and connected to transistor 2 in series. In transistor 2, when a voltage is applied to gate electrode 13, a channel is produced in silicon pillar 11, and a longitudinal cur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com