Method of manufacturing printed circuit board

a printed circuit board and manufacturing method technology, applied in the direction of metallic material coating process, synthetic resin layered products, pretreated surfaces, etc., can solve the problems of difficult realization of fine circuits with less than 50 m pitch (l/s=25/25 m), difficult to generate heat, etc., and achieve high-reliability fine circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

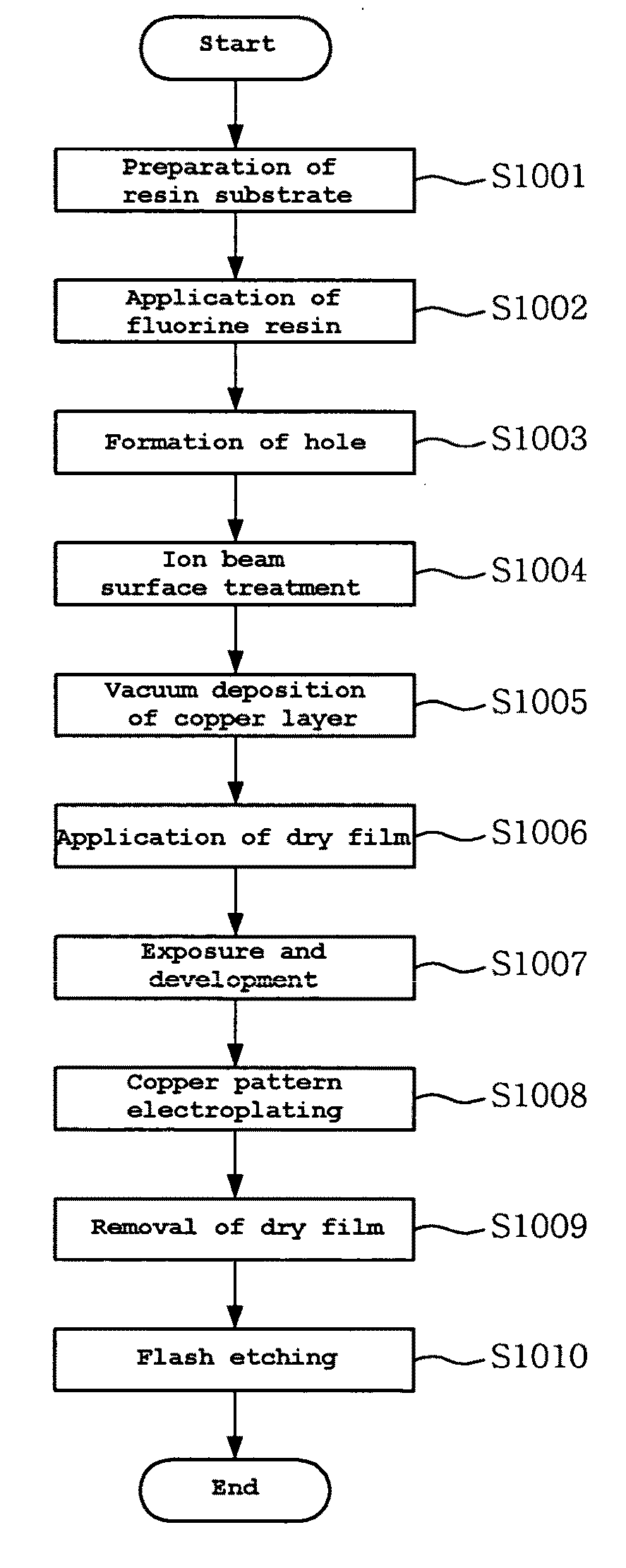

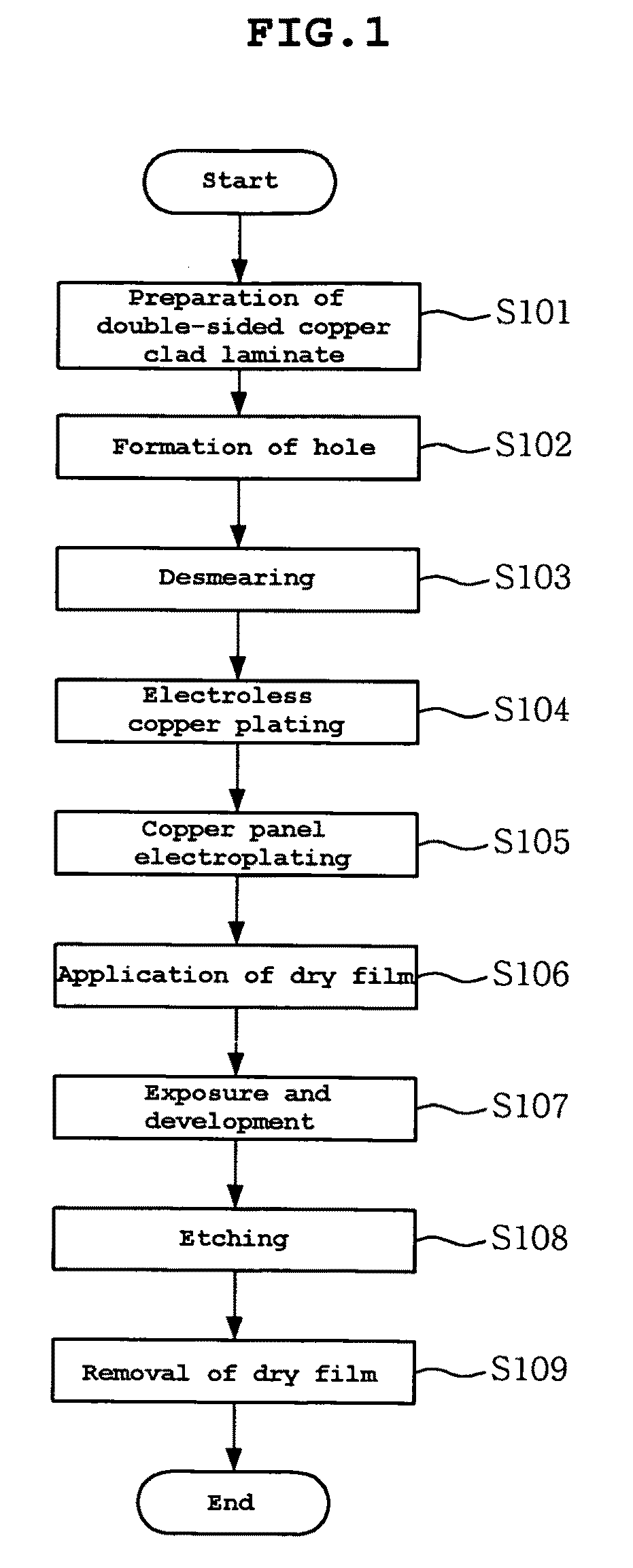

Method used

Image

Examples

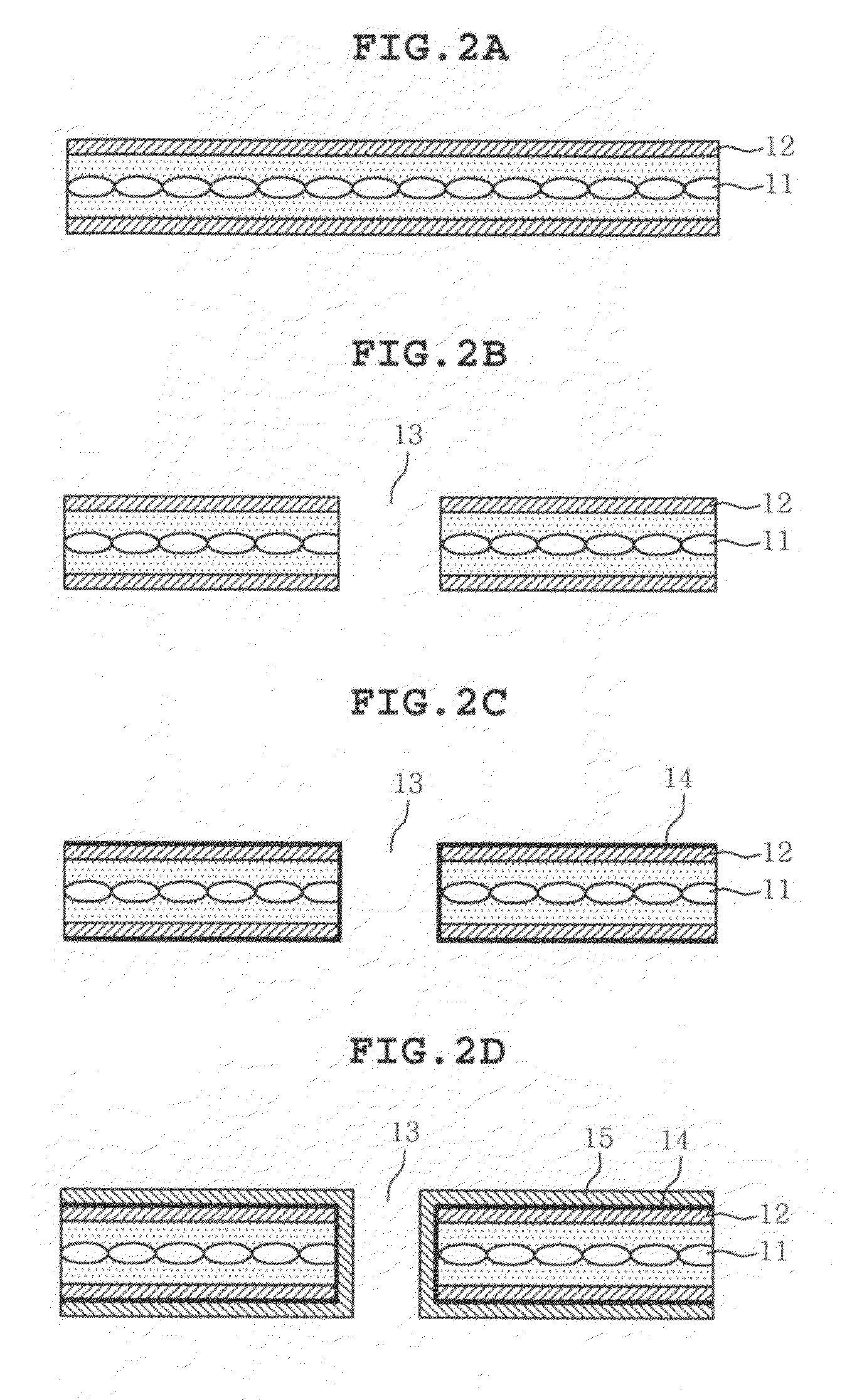

example 1

[0081]Both surfaces of a polyimide resin substrate, used as a base material, were coated several times with PTFE under conditions of a temperature of 350˜420° C. and humidity of

[0082]The peel strength and surface roughness of the PCB thus manufactured were measured. The results are shown in Table 2 below.

example 2

[0083]Both surfaces of a polyimide resin substrate, used as a base material, were coated several times with TPI under conditions of a temperature of 250˜350° C. and humidity of

[0084]The peel strength and surface roughness of the PCB thus manufactured were measured. The results are shown in Table 2 below.

PUM

| Property | Measurement | Unit |

|---|---|---|

| surface roughness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com