One terminal capacitor interface circuit

a capacitor and interface circuit technology, applied in the field of interface circuits, can solve the problems of low frequency noise, inability to easily correct the offset error of the integration amplifier, and the limitation of the circuit topologies that can be used, and achieve the effect of low frequency nois

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Aside from the preferred embodiment or embodiments disclosed below, this invention is capable of other embodiments and of being practiced or being carried out in various ways. Thus, it is to be understood that the invention is not limited in its application to the details of construction and the arrangements of components set forth in the following description or illustrated in the drawings. If only one embodiment is described herein, the claims hereof are not to be limited to that embodiment. Moreover, the claims hereof are not to be read restrictively unless there is clear and convincing evidence manifesting a certain exclusion, restriction, or disclaimer.

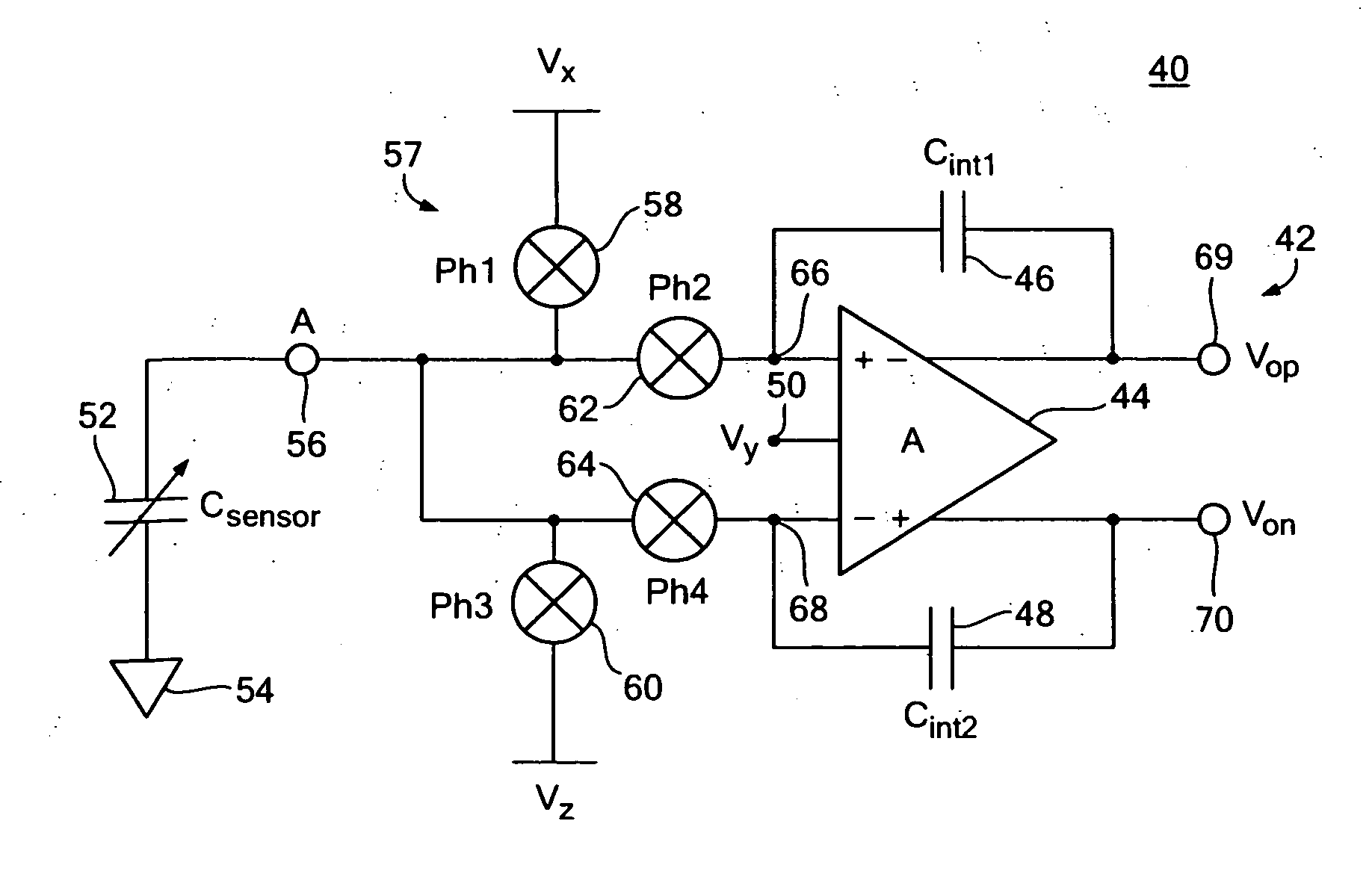

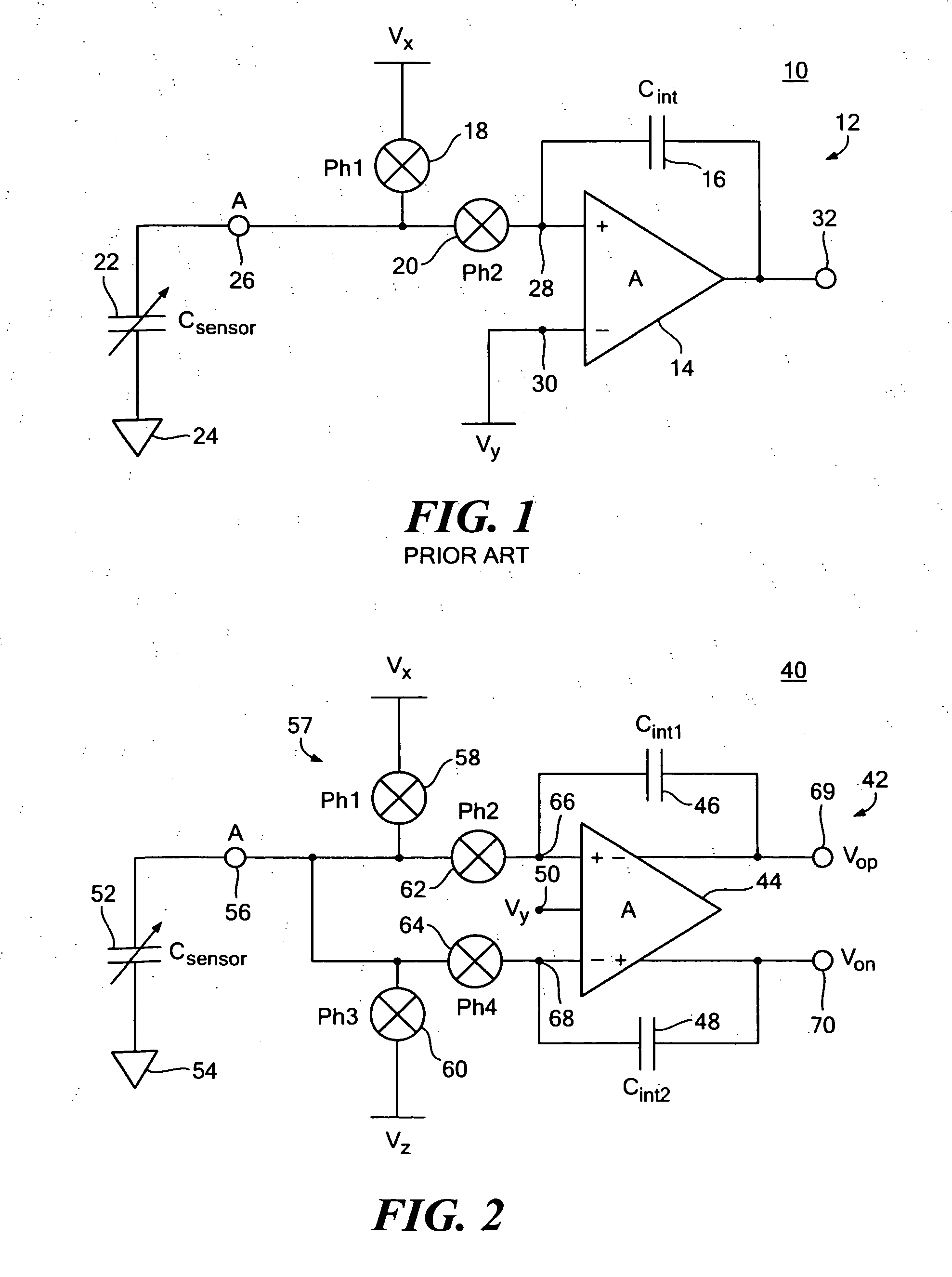

[0035] There is shown in FIG. 1, a conventional prior art one terminal capacitor interface circuit 10 which includes an integrating amplifier 12 including amplifier 14 with feedback or integrating capacitor Cint 16. Also included in interface circuit 10 are phased switches 18 and 20. The capacitor 22 whose capacitance is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com