Forming a semiconductor structure in manufacturing a semiconductor device using one or more epitaxial growth processes

a technology of epitaxial growth and semiconductor structure, which is applied in the field of semiconductor structure formation in the manufacture of semiconductor devices, can solve the problems of unsatisfactory stress in the semiconductor structure, and achieve the effect of reducing the disadvantages and eliminating the problems of previous techniques for forming semiconductor structure in the manufacturing of semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

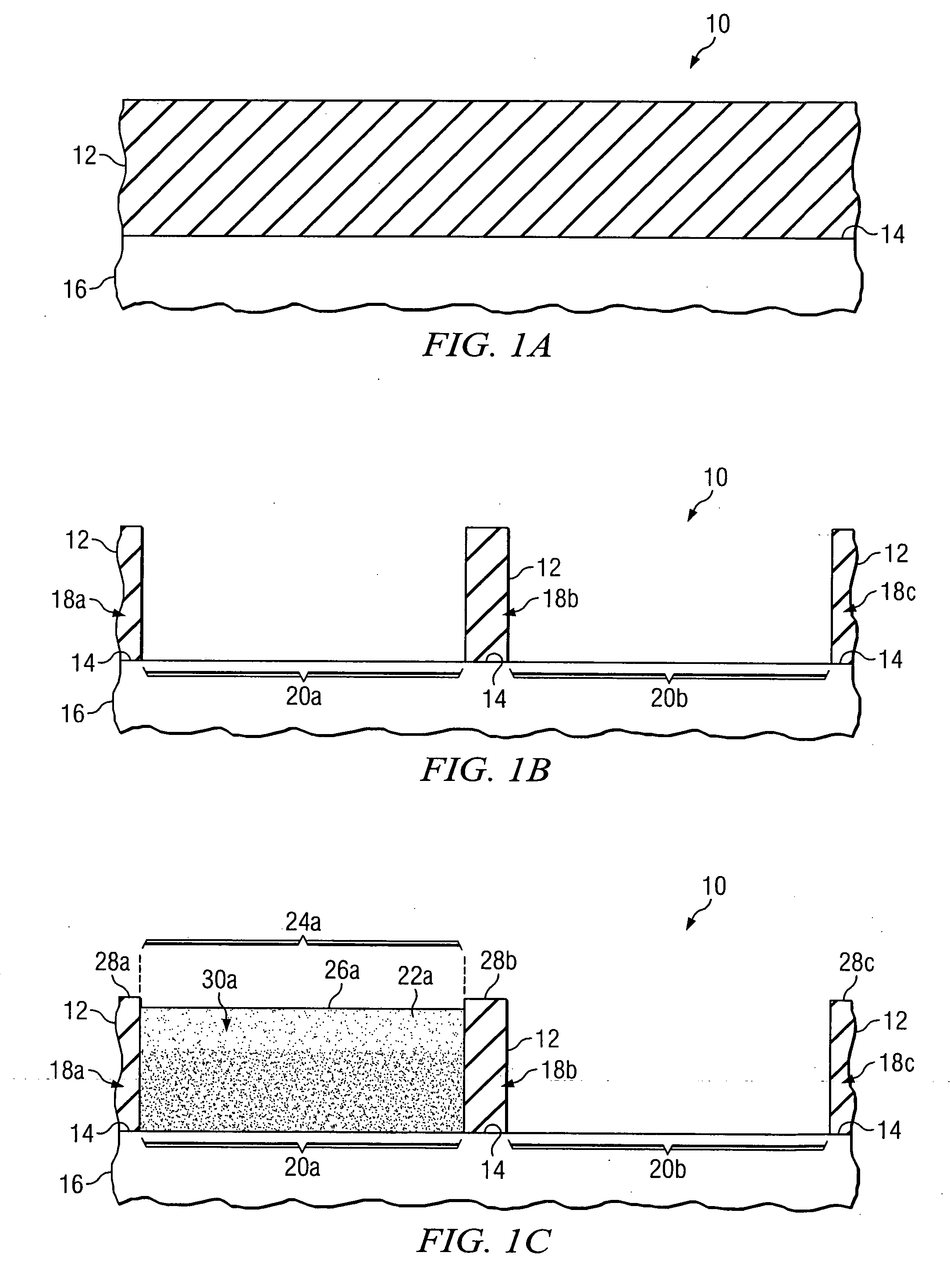

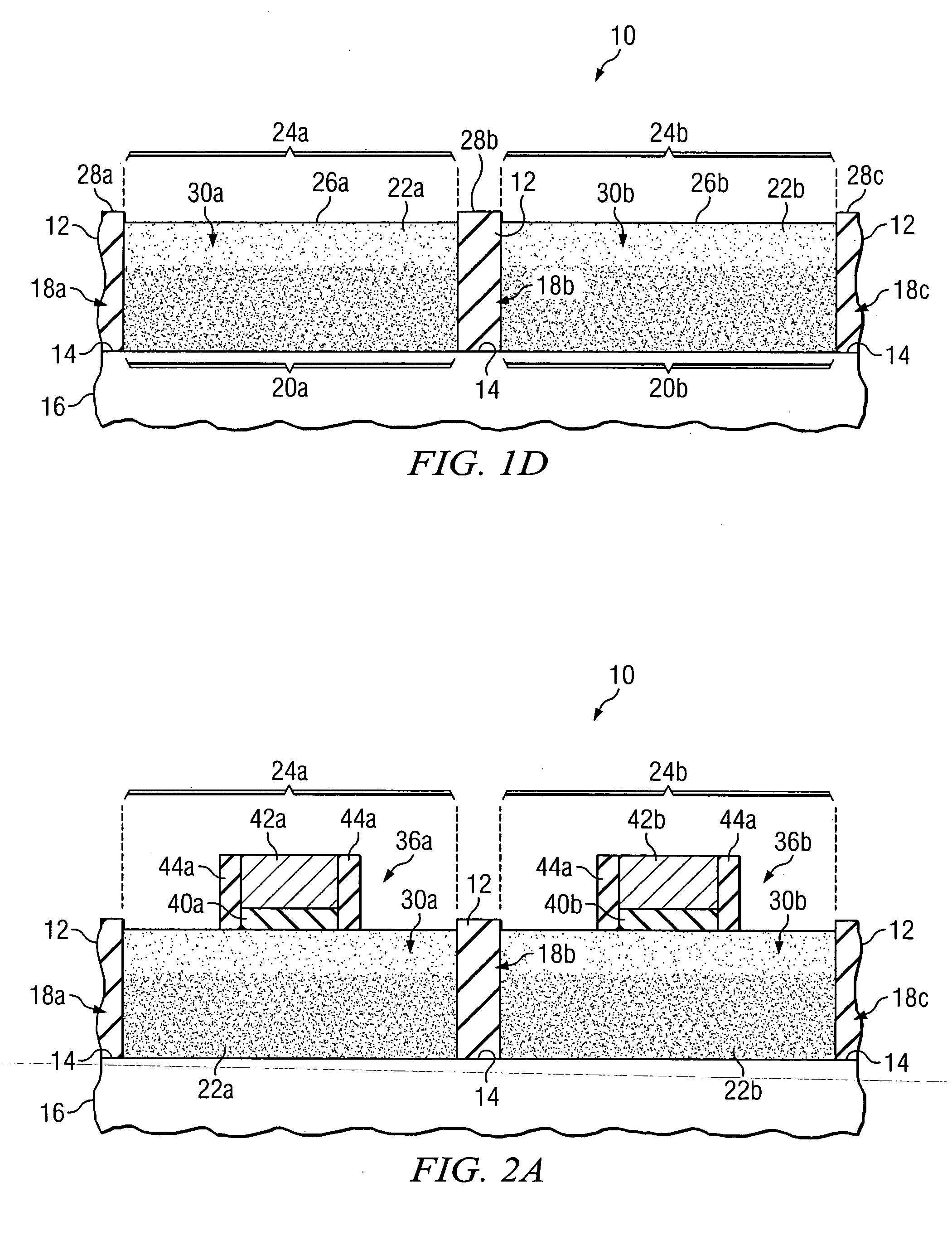

[0015]FIGS. 1A-1D illustrate an example process for forming a semiconductor structure 10 in manufacturing a semiconductor device, the semiconductor structure 10 formed using one or more epitaxial growth processes and having one or more isolation regions separating one or more active regions. In one embodiment, the semiconductor device includes a complementary metal oxide semiconductor (CMOS) device, such as a p-channel metal oxide semiconductor (PMOS) device or n-channel metal oxide semiconductor (NMOS) device.

[0016] As shown in FIG. 1A, an oxide layer 12 may be provided on a surface 14 of a silicon or other substrate layer 16. While surface 14 is illustrated as being substantially flat, surface 14 may have any suitable profile according to particular needs or manufacturing tolerances, for example. Oxide layer 12 may be grown on surface 14 of substrate layer 16 using any suitable technique, deposited on surface 14 of substrate layer 16 using any suitable technique, or otherwise pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com