Photomask and integrated circuit manufactured by automatically eliminating design rule violations during construction of a mask layout block

a technology of photomasks and integrated circuits, which is applied in the field of photolithography, can solve the problems of increasing the time needed to design the integrated circuit, layout designers may create design rule violations, and the layout process is complicated, and the disadvantages of eliminating design rule violations on the photomask have been substantially reduced or eliminated

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

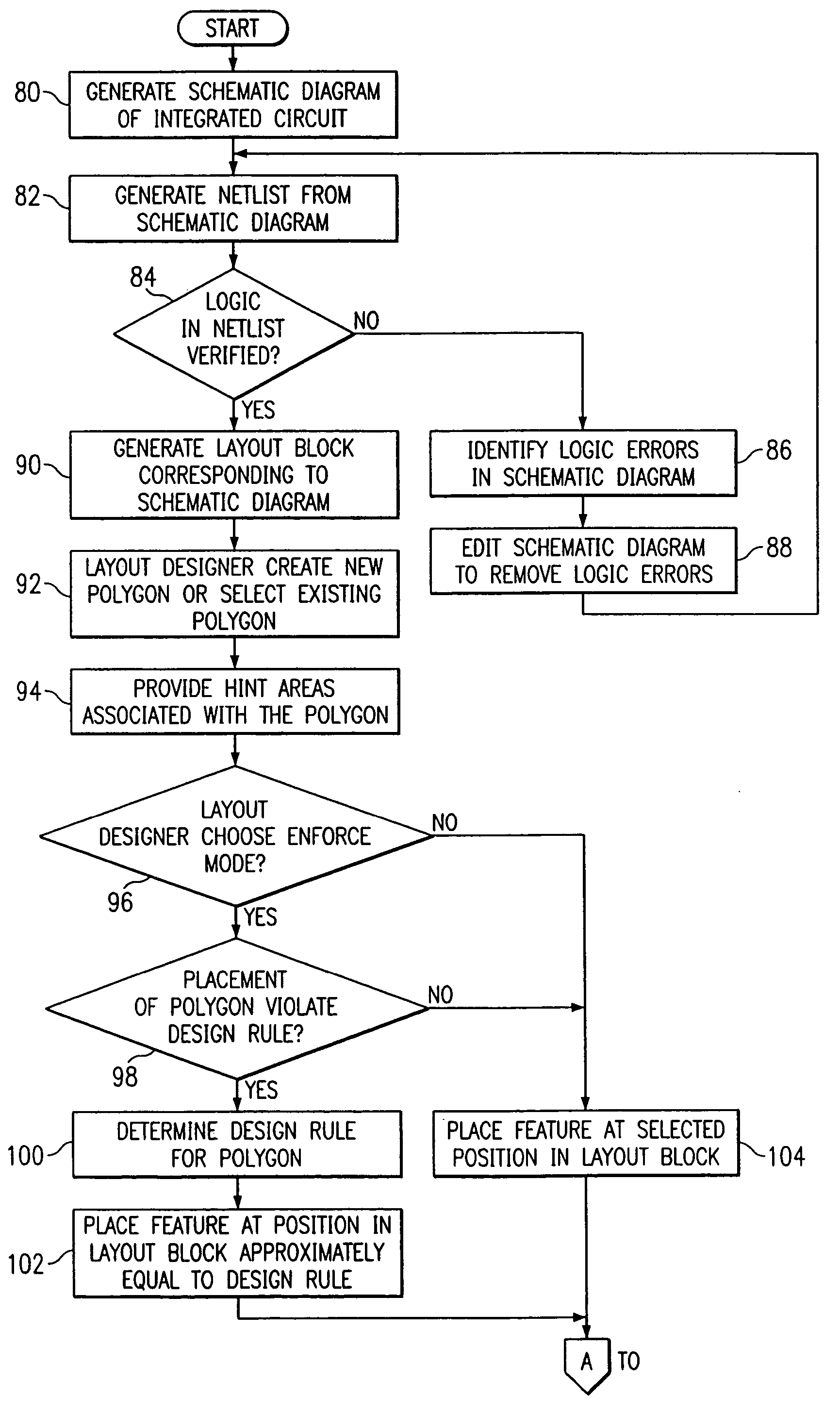

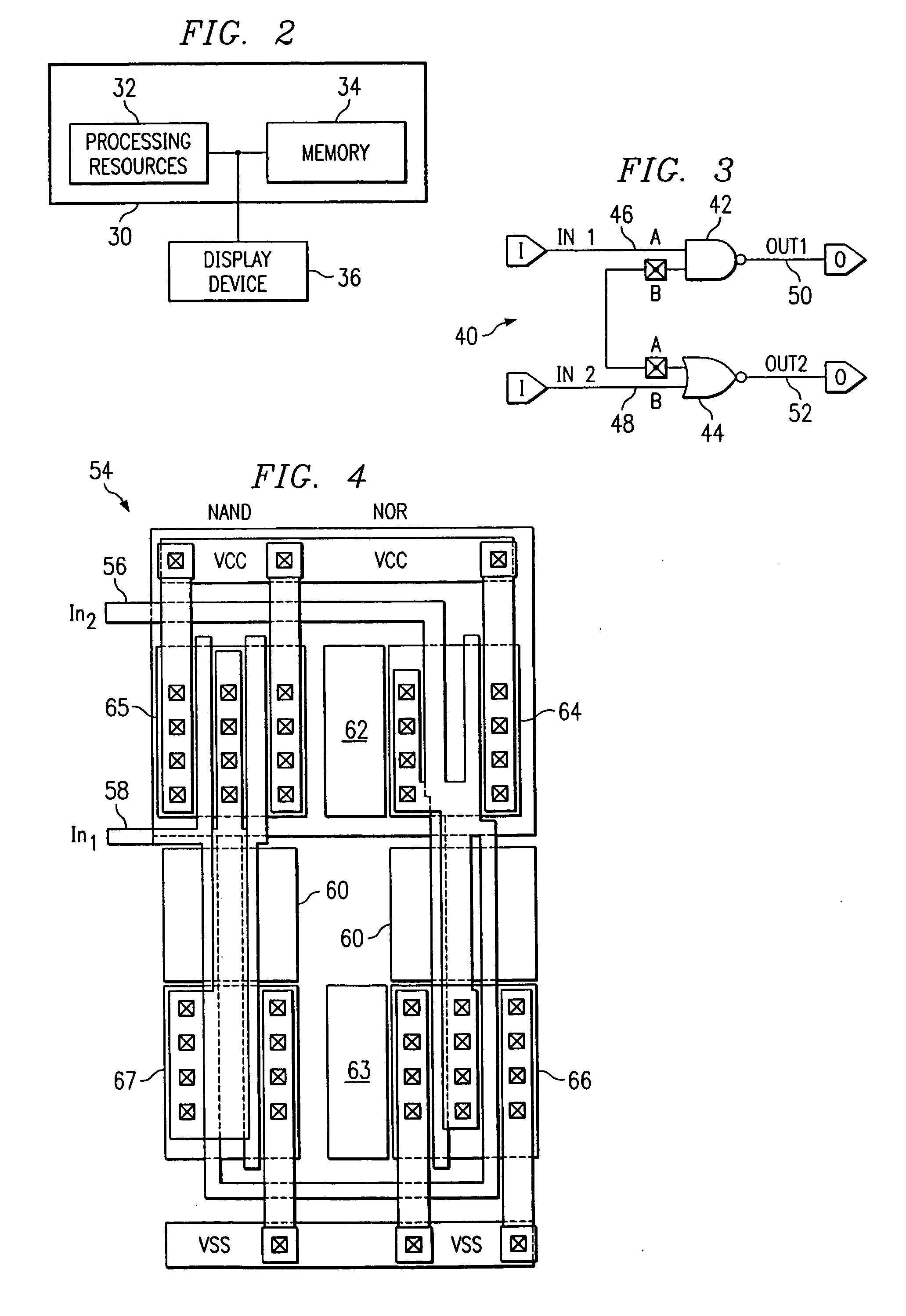

[0020] Preferred embodiments of the invention and its advantages are best understood by reference to FIGS. 1 through 6 of the drawings, like numerals being used for like and corresponding parts of the various drawings.

[0021] As the number of transistors on an integrated circuit continues to increase, the design process for the integrated circuit becomes more complex. For example, an increasing number of transistors may require additional layers to form the integrated circuit on a semiconductor wafer. Each layer of the integrated circuit may have one or more design rules that define how polygons on each layer should be placed in a mask layout block for a desired manufacturing process. The number of design rules for the desired manufacturing process, therefore, increases with the number of layers formed on the semiconductor wafer.

[0022] A design rule typically defines the minimum or maximum allowable dimension for a feature fabricated on a specific layer of the integrated circuit. F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com