Solid imaging device

A solid-state imaging device, pixel technology, applied in radiation control devices, signal generators with a single pickup device, image communication, etc., can solve the problem of reduced storage time, fewer photoelectric conversion elements, and shorter storage time. problem, to prevent the reduction of sensitivity, to achieve high image quality, and to achieve the effect of high practical value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

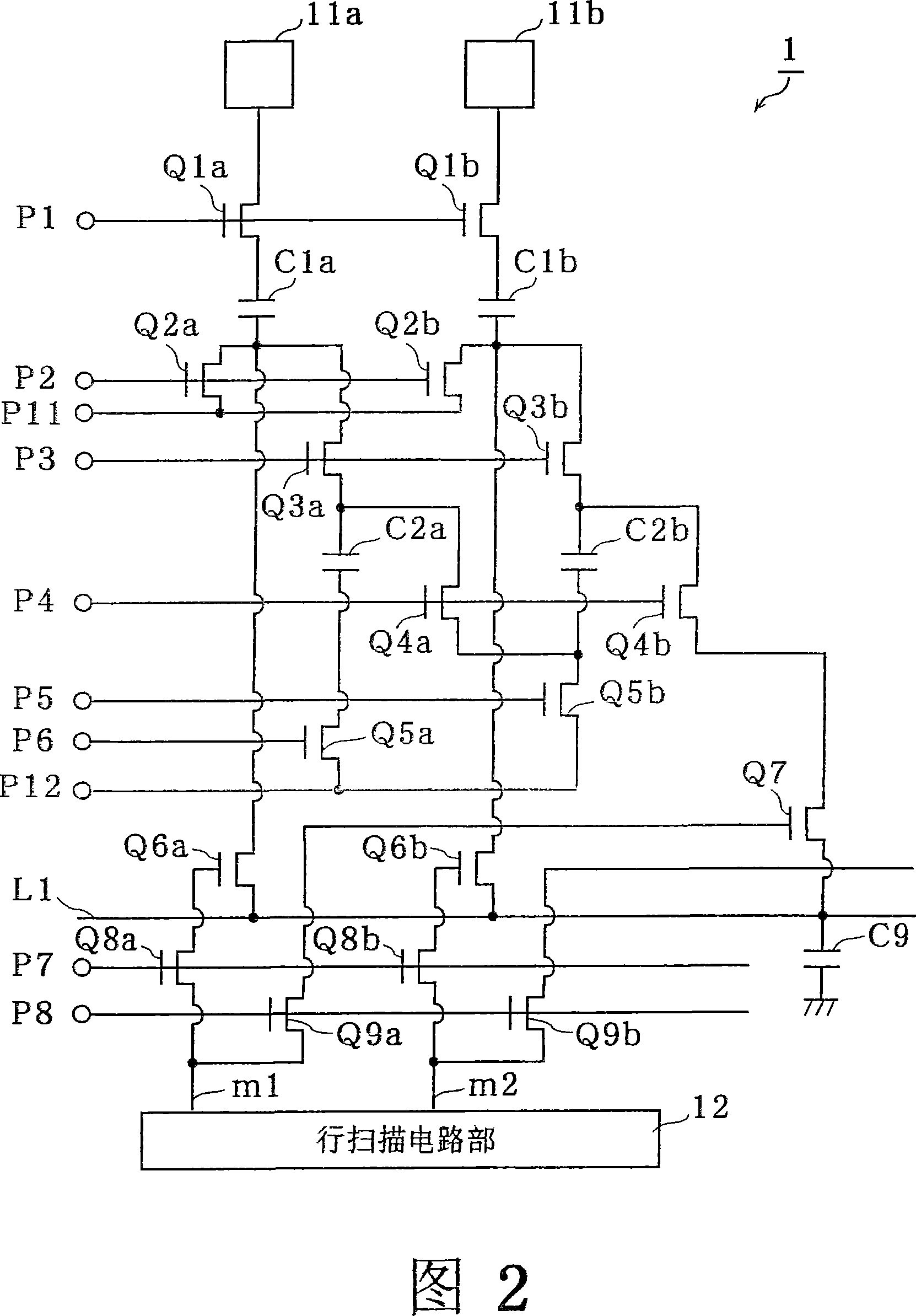

[0062] FIG. 2 is a schematic diagram showing the circuit configuration of the solid-state imaging device according to the first embodiment. In addition, the example shown in this figure shows the case where there are two pixel parts (photoelectric conversion elements) arranged in the row direction.

[0063] As shown in FIG. 2, the solid-state imaging device 1 includes: pixel sections 11a and 11b; a plurality of MOS transistors Q1a, Q1b, Q2a, Q2b, Q3a, Q3b, Q4a, Q4b, Q5a, Q5b, Q6a, Q6b, Q7, Q8a, Q8b, Q9a, Q9b; a plurality of capacitors C1a, C1b, C2a, C2b; row scanning circuit section 12; drive pulse application terminals P1, P2, P3, P4, P5, P6, P7, P8 to which drive pulse application terminals Drive pulses from the column scanning circuit section or signal readout circuit section not shown; bias voltage application terminals P11 and P12 to which the bias voltage from the column scanning circuit section or the signal readout circuit section is applied ; And the signal output li...

Embodiment approach 2

[0099] Next, another solid-state imaging device according to the present invention will be described.

[0100] FIG. 7 is a circuit diagram showing the configuration of the solid-state imaging device shown in the second embodiment. Here, as described above, in the solid-state imaging device 1, since the signal value output to the signal output line L1 is divided by the capacitor C9, there is a loss.

[0101] Therefore, as shown in FIG. 7 , the solid-state imaging device 2 according to the second embodiment includes, in addition to the structure of the solid-state imaging device 1, a high input impedance circuit 13 connected to the MOS transistor Q4b between the source and the drain of the MOS transistor Q7.

[0102] As a result, the value of the signal output to the signal output line L1 is not divided by the capacitor C9, and in the case of the memory circuit having the two structures of FIG. 7, the signal value is 2*Vt, and in the case of having N memory circuits Next, the ...

Embodiment approach 3

[0110] Next, another solid-state imaging device of the present invention will be described.

[0111] 9 is a circuit diagram showing the configuration of the solid-state imaging device according to the third embodiment. As shown in FIG. 9 , the solid-state imaging device 3 is applicable when two pixel sections (photoelectric conversion elements) are arranged in the column direction, and the solid-state imaging device 3 includes pixel sections 30 a and 30 b , and MOS transistors Q1 , Q2 , and Q6 . , Q11a, Q11b, Q12a, Q12b, Q13a, and Q13b; capacitors C1, C3a, C3b; buffer 31; row scanning circuit section 32; Pressure application terminals P31 and P32; and signal output lines L2 and L3, etc.

[0112] The pixel portions 30a and 30b include a photoelectric conversion element, a charge transfer portion, a charge-to-voltage conversion portion, a voltage amplifying portion, and the like. In FIG. 9, the detailed circuit configuration of the pixel sections 30a and 30b is omitted.

[01...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com