Semiconductor element and formation method

A semiconductor and component technology, applied in the field of semiconductor components, can solve problems such as difficult control, and achieve the effect of reducing time and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the above-mentioned and other objects, features, and advantages of the present invention more obvious and understandable, the preferred embodiments are specifically cited below, together with the accompanying drawings, and are described in detail as follows:

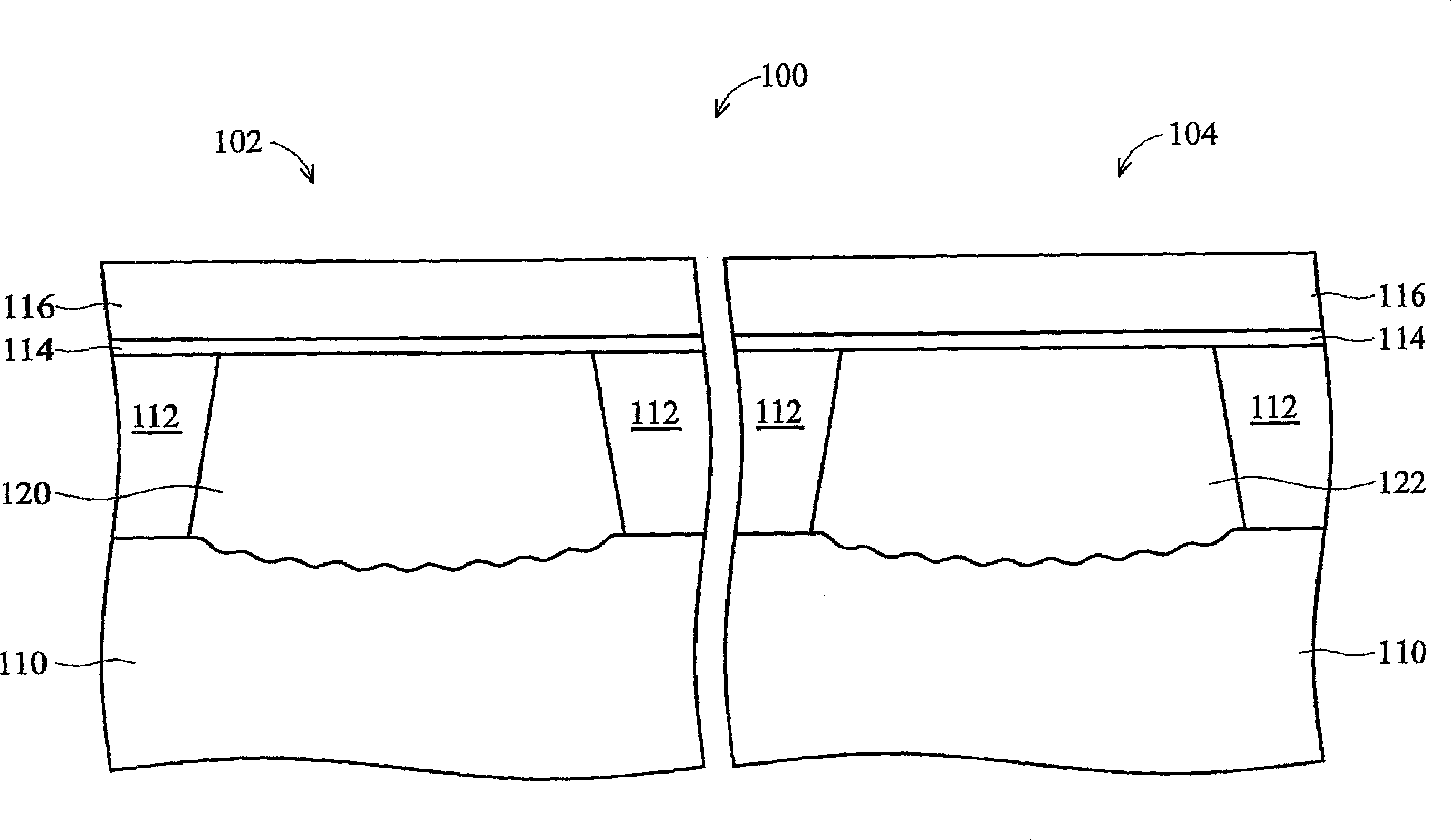

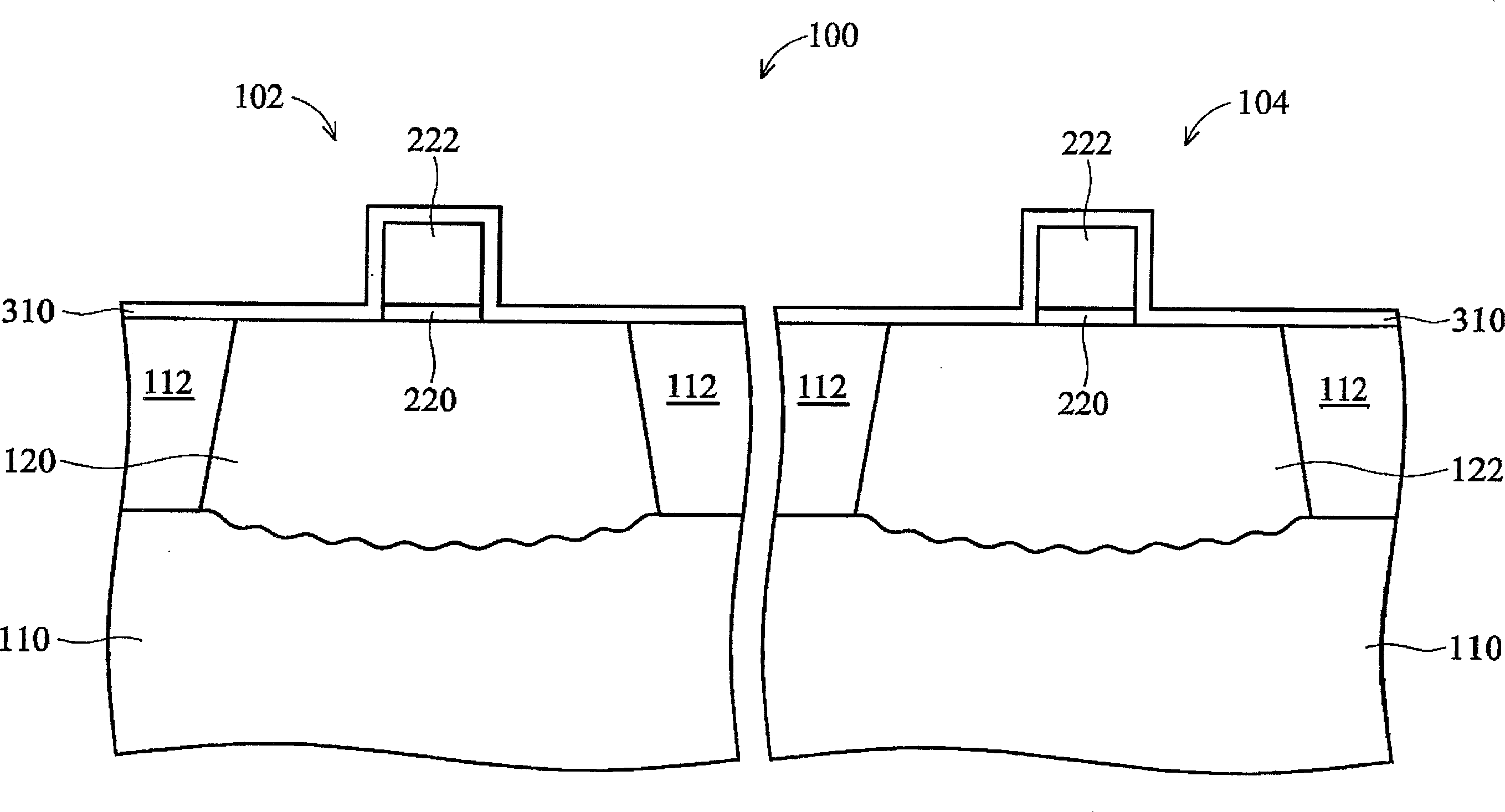

[0034] Figure 1 to Figure 6 It is shown that the present invention utilizes compensating spacers to fabricate an NMOS and a PMOS. The present invention can be applied to various circuits. For example, I / O components, core components, memory components, system-on-chip (SoC) components, or other integrated circuits. The invention can be generally applied to the process below 65 nanometers where the short channel effect often occurs.

[0035] see figure 1 , the wafer 100 includes a substrate 110 having an NMOS region 102 and a PMOS region 104 . In this embodiment, the substrate 110 includes a P-type bulk silicon substrate, a P-type well 120 is formed in the NMOS region 102 and an N-type well 122...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com