Low delay temp compensation bias circuit for TDD mode

A technology of temperature compensation and time-division duplexing, which is applied to improving amplifiers to reduce temperature/power supply voltage changes, electrical components, transmission systems, etc. It can solve problems such as large time constants, uncertainties, and insufficient compensation to achieve electrical performance. Effects of unaffected and stable bias voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

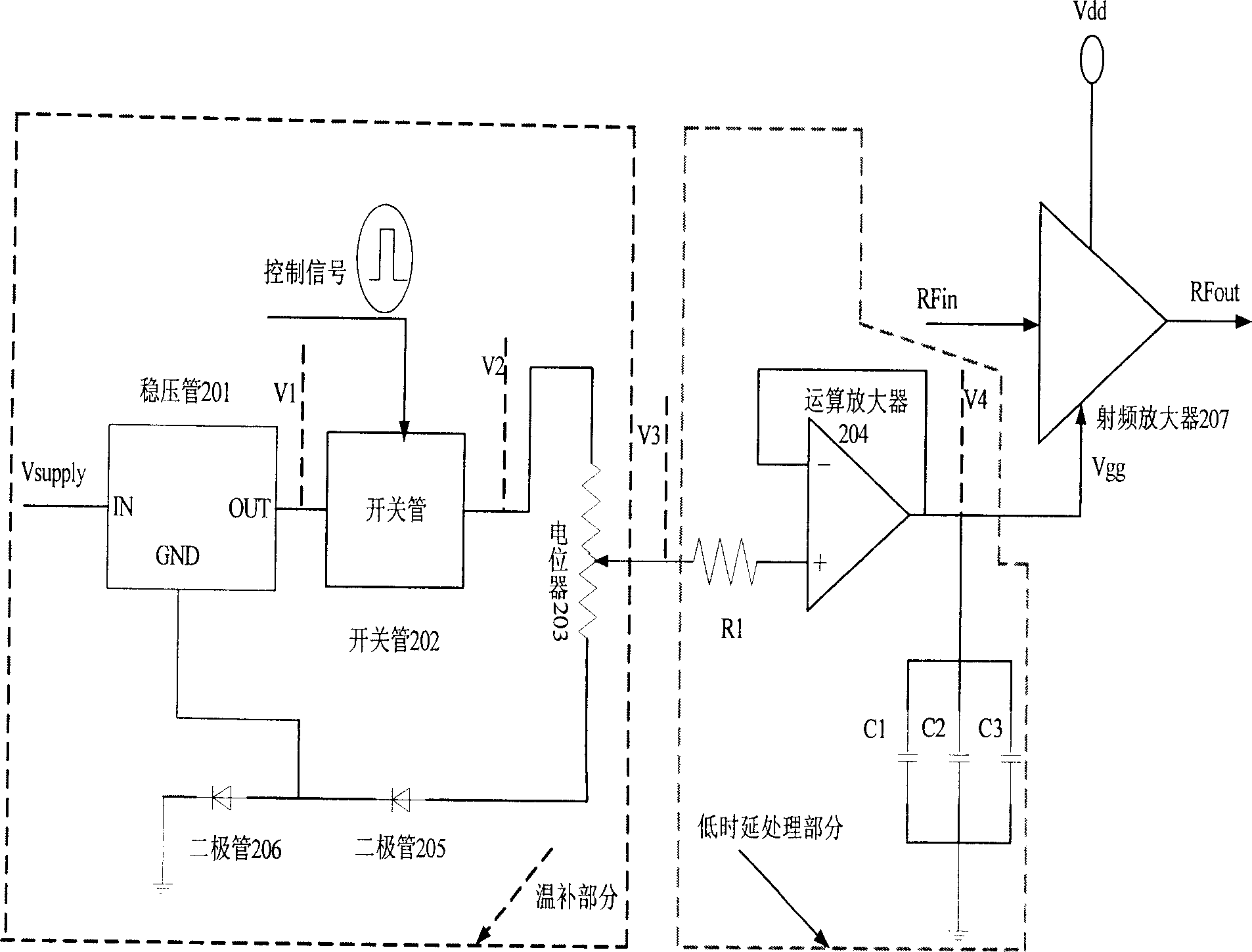

[0033] figure 2 A schematic diagram of the low-latency temperature compensation bias circuit for TDD mode of the present invention is shown.

[0034] Such as figure 2 As shown, the low time-delay temperature compensation bias circuit of the present invention is mainly composed of a voltage regulator tube, a switch tube, a potentiometer, an operational amplifier and a diode.

[0035] The circuit consists of two parts, the temperature compensation part formed by the closed loop circuit in front of V3, and the low delay processing part between V3 and Vg.

[0036] from figure 2 It can be seen that the input voltage Vsupply passes through the regulator tube 201 to generate a stable voltage V1, and when the ambient temperature changes, the voltage remains basically unchanged, reducing the instability of the subsequent circuit voltage. The voltage V1 is input into the switch tube 202, and under the action of the control signal (TTL signal), a pulse voltage V2 that changes with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com