Semiconductor device and method for making same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as inability to operate transistors, deterioration of transistor characteristics, deviation of gate electrode resistance, etc., achieve high yield, and prevent carbon pollution , the effect of suppressing in-plane deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

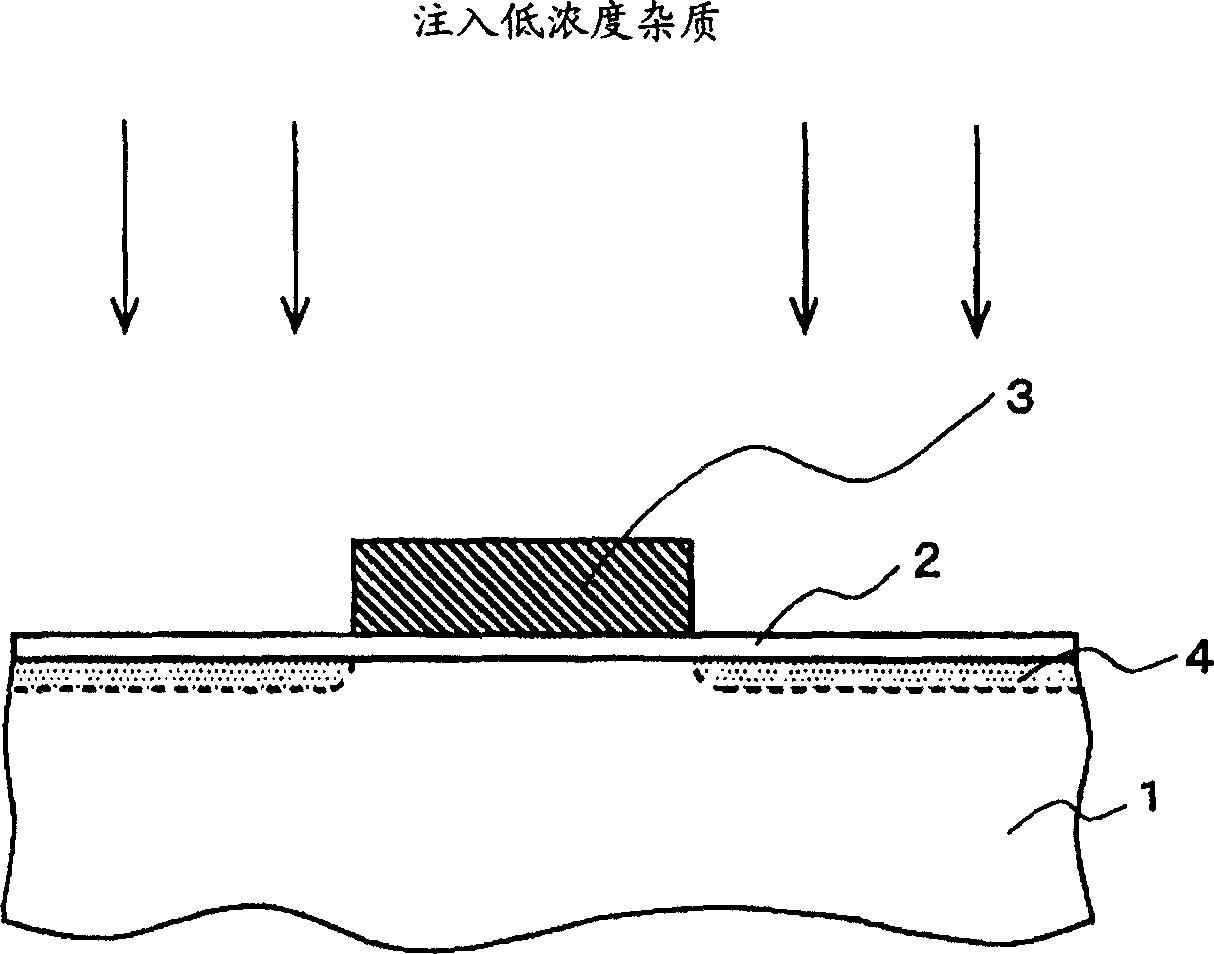

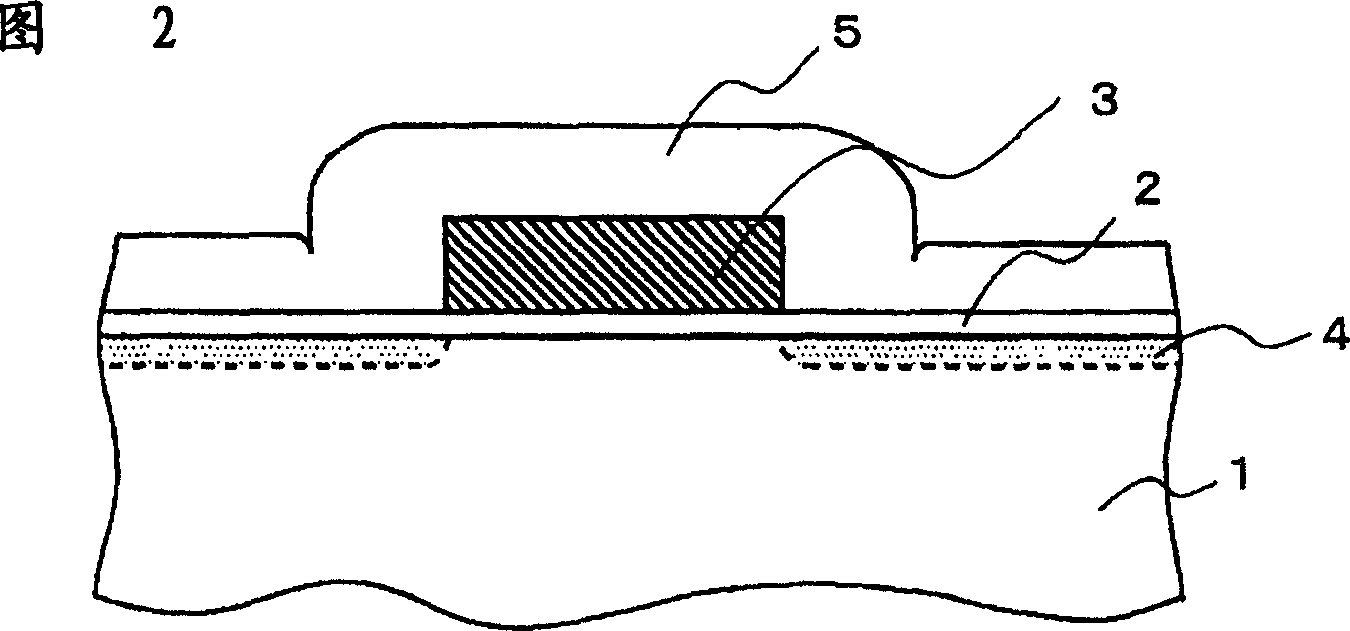

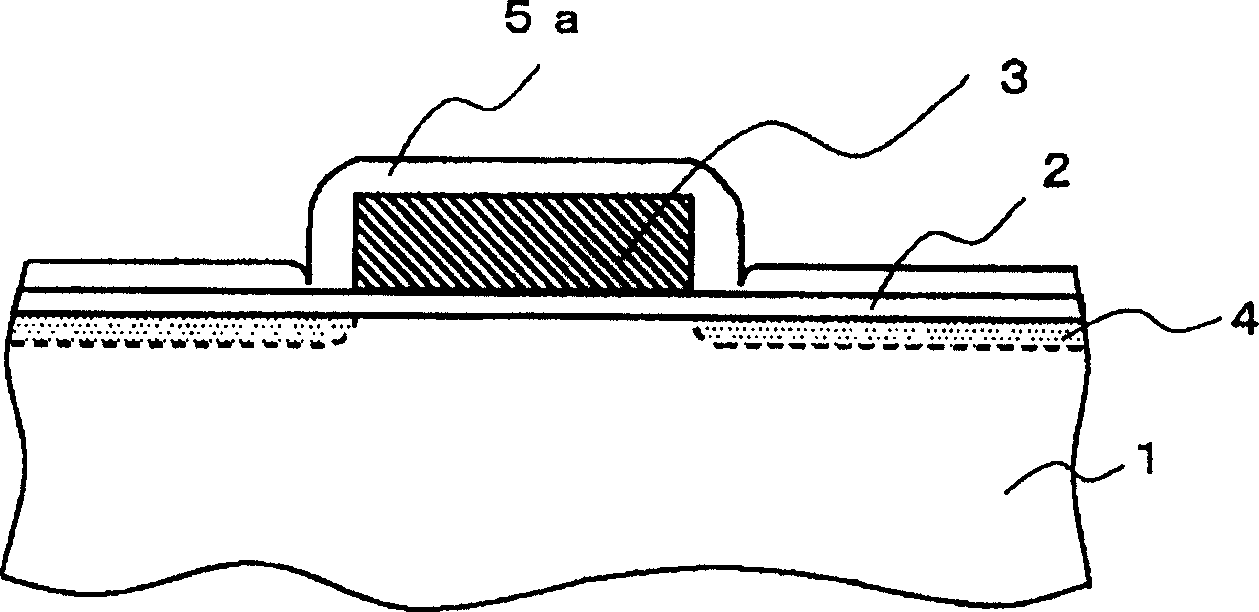

[0042] refer to figure 1 ˜ FIG. 8 illustrate the manufacturing method of the semiconductor device of the present invention.

[0043] refer to figure 1 A silicon oxide film obtained by a thermal oxidation method with a film thickness of about 5 nm was formed on the silicon substrate 1 . This is used as the gate insulating film 2 . Further, a polysilicon film having a film thickness of approximately 200 nm is formed on the gate insulating film 2 . This is processed by photolithography and etching to form gate electrode 3 .

[0044] In addition, although not shown, there is also a method of forming a silicon oxide film or the like on the polysilicon film and using it as a hard mask in order to perform etching with excellent precision.

[0045] Then, using the gate electrode 3 as a mask, for example, phosphorous ions can be used, and the implantation dose is 1 to 5×10 14 (Number of ions / cm 2 ) level of low-concentration impurity, forming low-concentration impurity region 4...

PUM

| Property | Measurement | Unit |

|---|---|---|

| coating thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com