Zero-delay buffer circuit for spread spectrum clock system and method

A spread spectrum clock and buffer circuit technology, applied in transmission systems, digital transmission systems, electrical components, etc., can solve the problems of jitter and phase offset limiting clock frequency, phase offset error, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

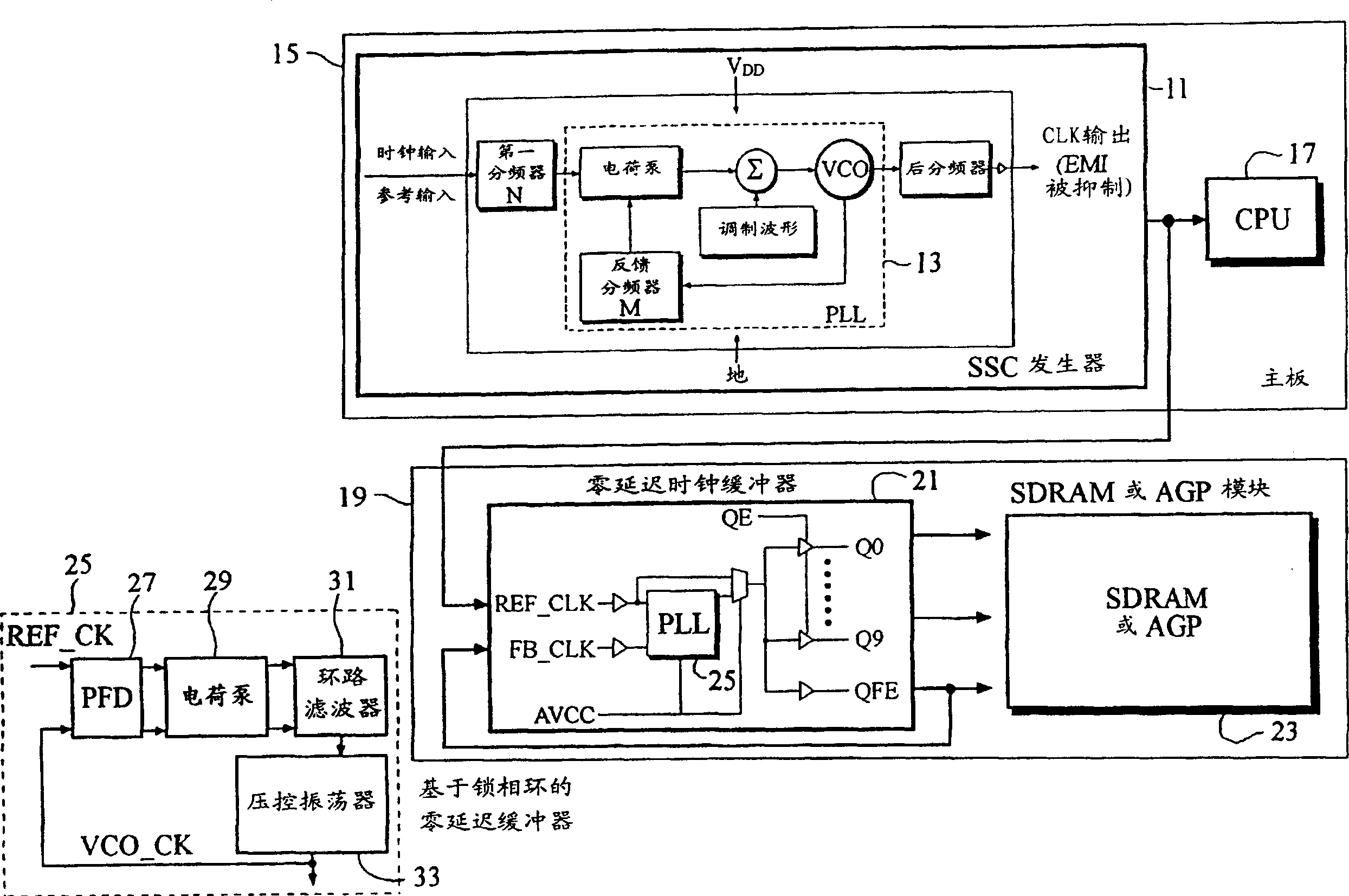

[0045] Figure 8 A block diagram of a spread spectrum clock system circuit in accordance with a preferred embodiment of the present invention is illustrated. These include a main board 83 , an SSC generator 73 , a PLL circuit 81 and a CPU 77 . The peripheral board 75 includes a zero-delay clock buffer circuit 68 with a delay locked loop (DLL) circuit 69 . Zero-delay clock buffer circuit 68 receives the FM clock signal from SSC generator 73 and provides an output clock signal to peripherals 76 (eg, SDRAM, accelerated graphics port, etc.). The DLL circuit 69 includes: a phase detector 71 , a charge pump 72 , a loop filter 73 and a voltage-controlled delay chain (VCDC) circuit 74 .

[0046] Figure 9 A block diagram of DLL circuit 69 is illustrated in accordance with a preferred embodiment of the present invention. The DLL circuit 69 includes a first time-to-digital converter (TDC) 85 connected to the first register 87 , and a second TDC 89 connected to the second register 91...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com