Method of epitaxial bipolar device and complementary metallic oxide semiconductor device

A bipolar device and device technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as protecting CMOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

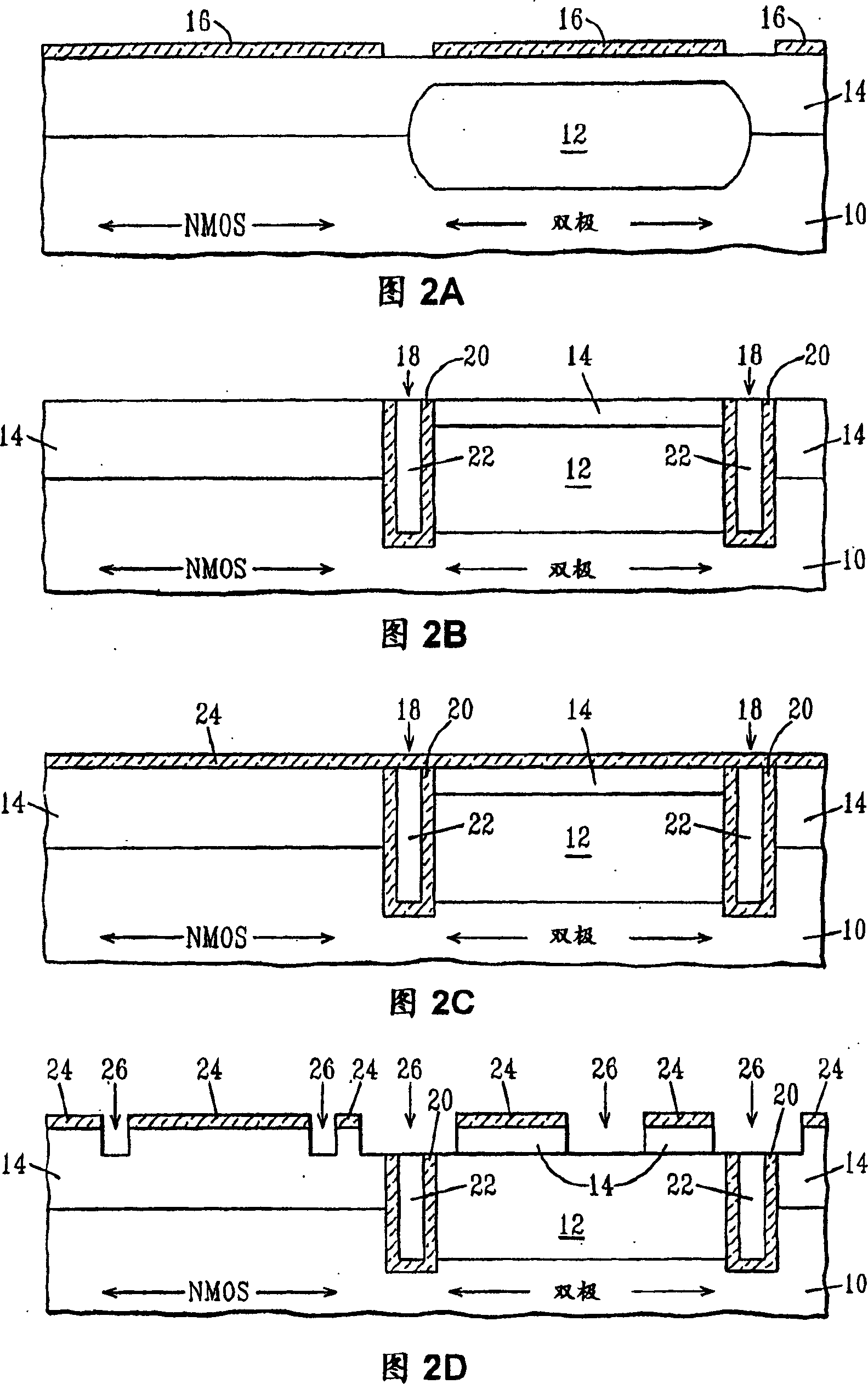

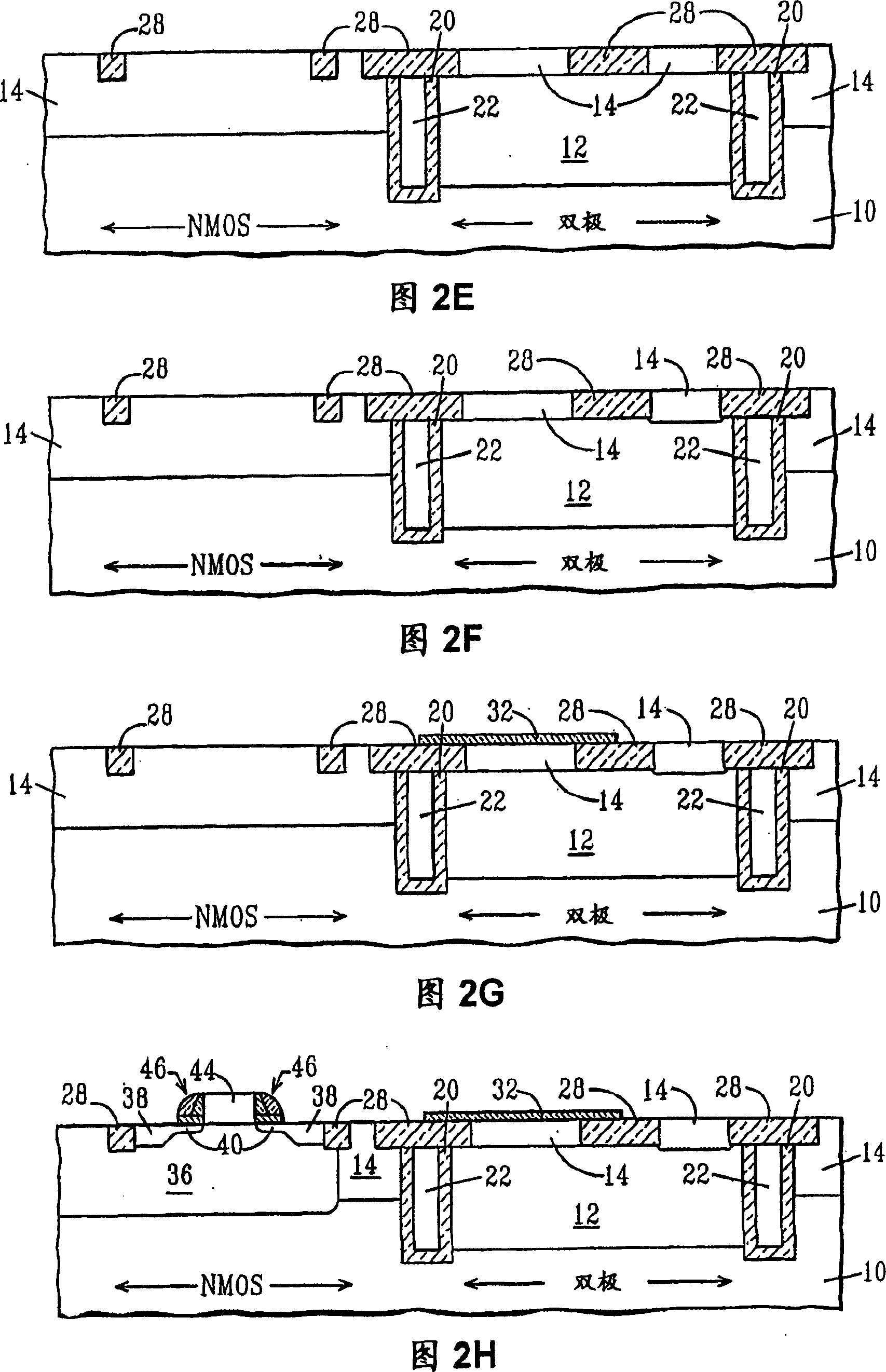

[0024] The present invention providing a method for fabricating a BiCMOS integrated circuit using a gate-last-base processing scheme will be described in more detail below with reference to the accompanying drawings of the present application. It should be noted that in the various figures, like or corresponding parts are denoted by like reference numerals.

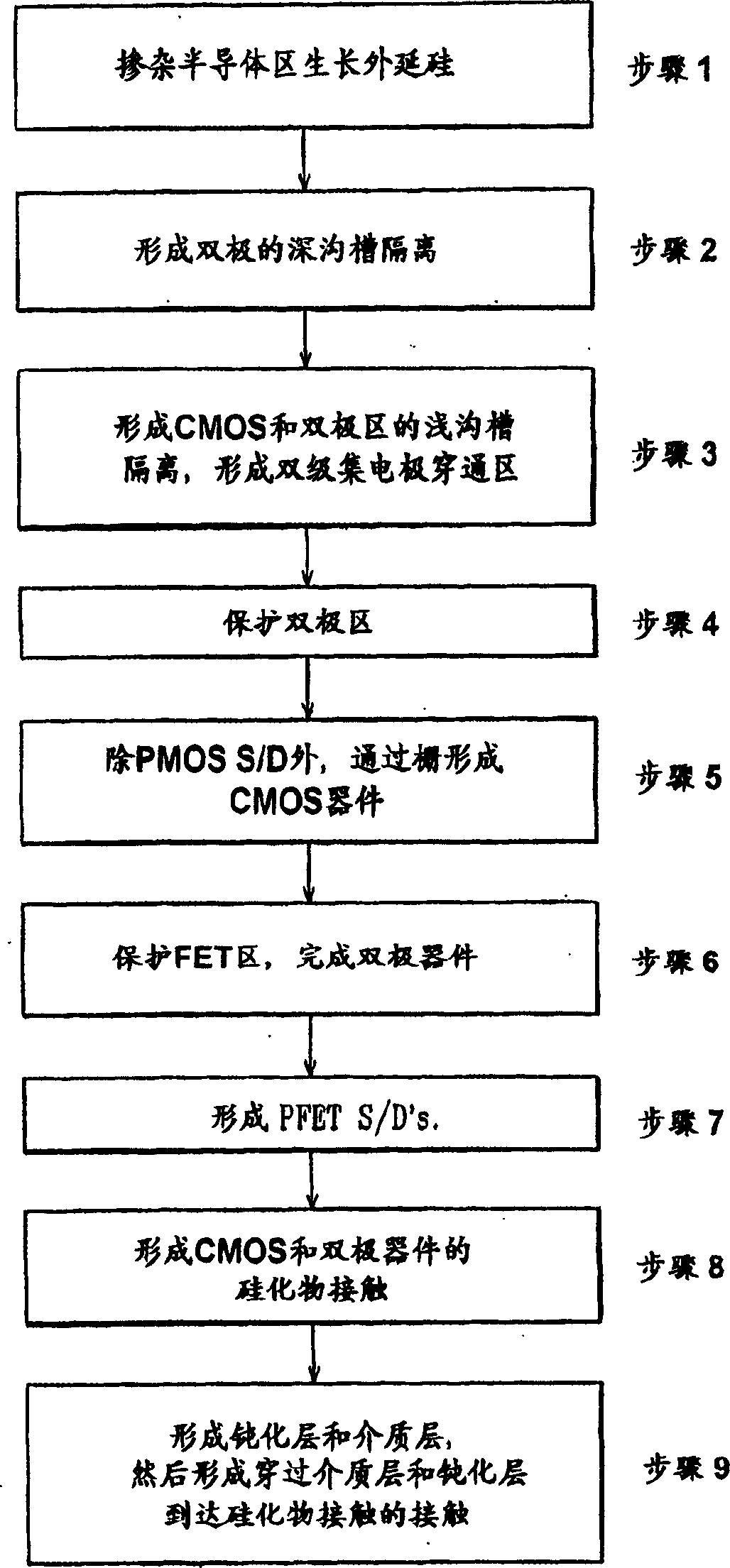

[0025] First, see figure 1 , which is a flow chart showing the basic processing steps of the integration scheme of the present invention. The steps shown in the flowcharts are described in greater detail below in conjunction with FIGS. 2A-2M and the discussion below.

[0026] As shown in Figures 2A-2M, these figures are cross-sectional views of various processing steps employed in the present invention in the fabrication of BiCMOS structures including bipolar and NMOS devices. Although NMOS devices are shown and described, the present invention can be used to fabricate PMOS devices. In an embodiment where a PMOS device...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com