High-voltage integrated power semiconductor device and manufacturing method thereof

A technology that integrates power and manufacturing methods. It is used in semiconductor/solid-state device manufacturing, semiconductor devices, and electrical components. It can solve problems such as difficulty in effectively improving device breakdown voltage, optimize vertical electric field distribution, improve vertical withstand voltage, and improve The effect of restriction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

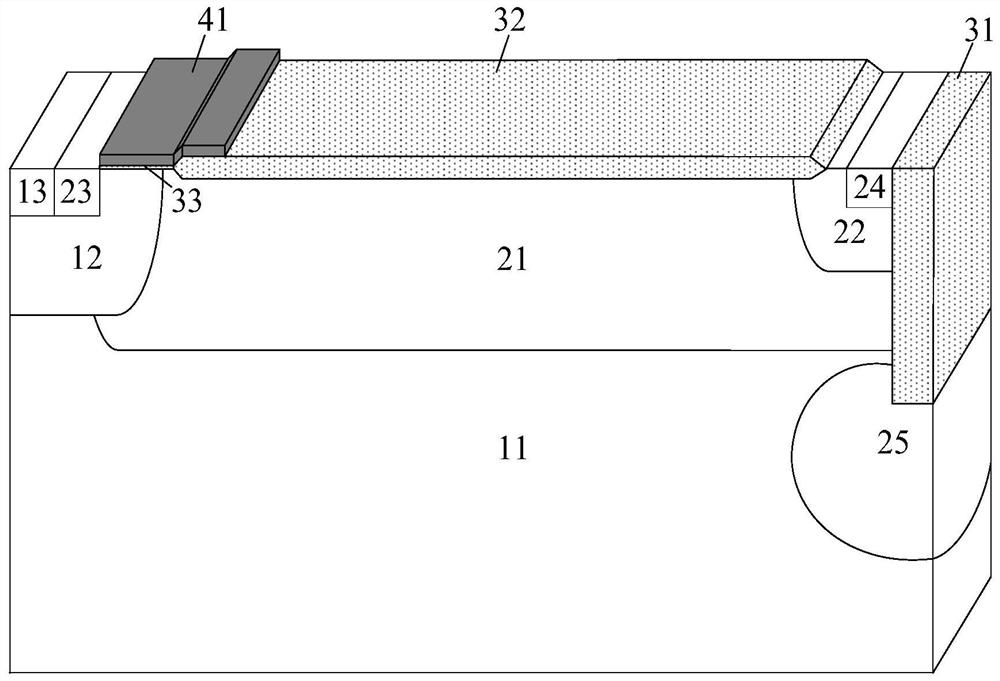

[0063] A high-voltage integrated power semiconductor device described in Embodiment 1, such as figure 1 shown, including:

[0064] First conductivity type substrate 11, second conductivity type drift region 21, first conductivity type well region 12, second conductivity type well region 22, first conductivity type heavily doped region 13, second conductivity type heavily doped region A23, the second conductive type heavily doped region B24, the second conductive type buried layer 25, the first dielectric layer 31, the second dielectric field oxide layer 32, the third dielectric gate oxide layer 33, and the control gate polysilicon electrode 41;

[0065] The first conductive type well region 12 is located on the left side of the second conductive type drift region 21 and is adjacent to it, and is connected to the first conductive type substrate 11 , and the second conductive type well region 22 is located in the second conductive type drift region. On the right side of and adj...

Embodiment 2

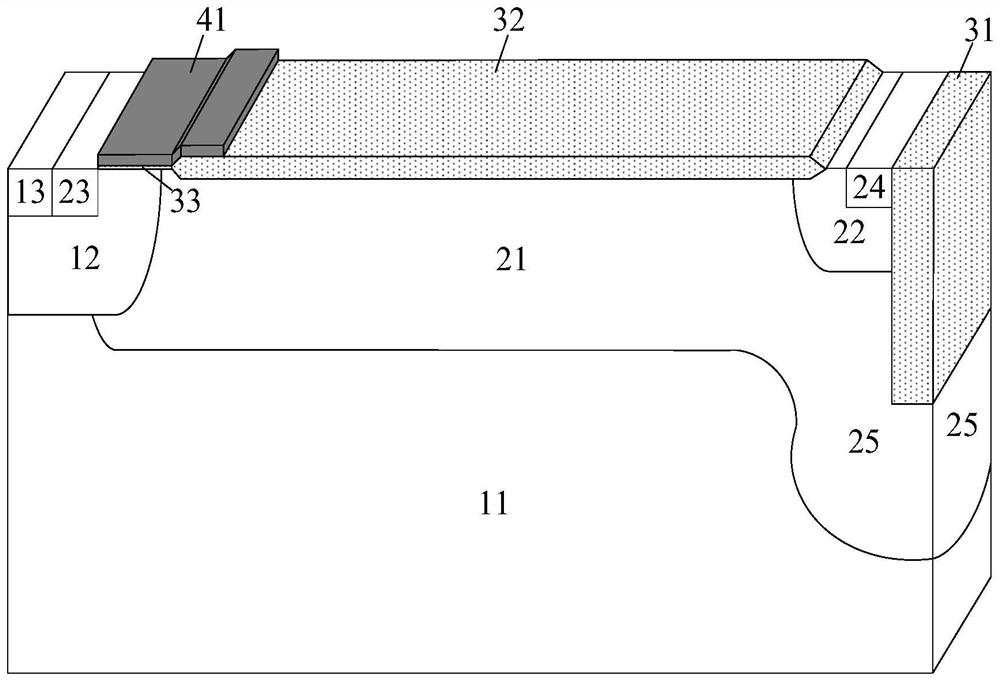

[0084] like figure 2 As shown, it is a schematic structural diagram of a high-voltage integrated power semiconductor device of Embodiment 2. The structure of this embodiment is different from that of Embodiment 1 in that the second conductive type buried layer 25 is connected to the second conductive type drift region 21, and its working principle is the same as Example 1 is basically the same.

Embodiment 3

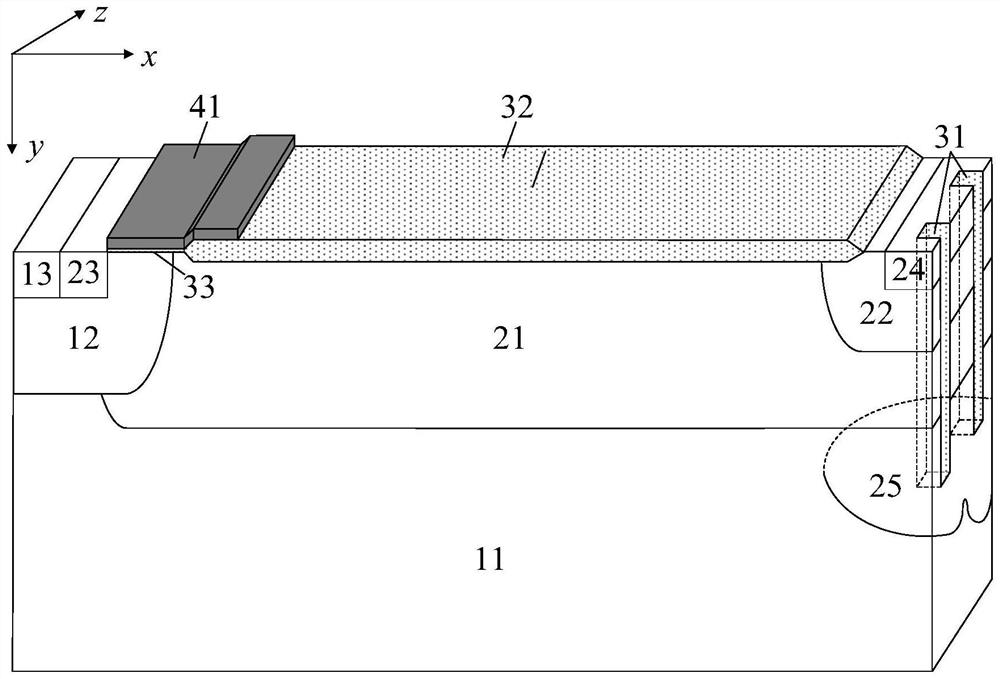

[0086] like image 3 As shown, it is a schematic structural diagram of a high-voltage integrated power semiconductor device of Embodiment 3. The structure of this embodiment is different from that of Embodiment 1 in that the dielectric grooves are located in the heavily doped region B24 of the second conductivity type, and are arranged discretely in the Z direction. Its working principle is basically the same as that of Example 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com