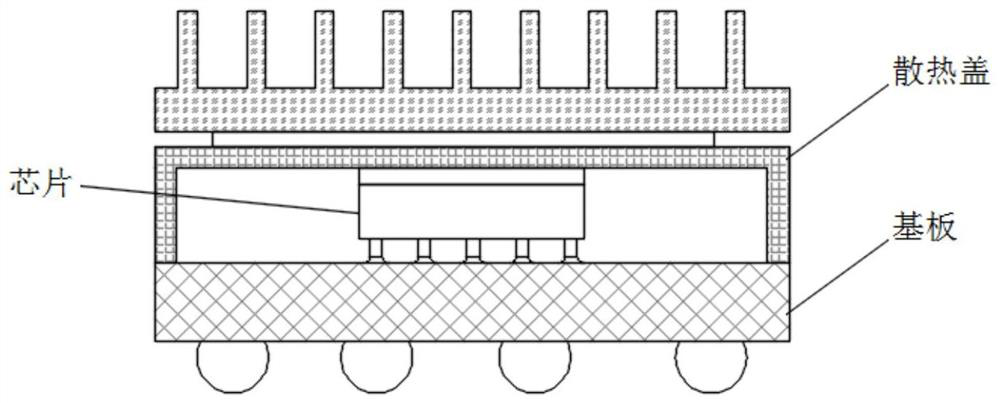

Chip packaging method and packaging structure

A chip packaging structure and chip packaging technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of high cost of mold opening, low production efficiency, increased production cycle, etc., to achieve a good working environment, reduce the overall thermal The effect of resistance and good electrical channel

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

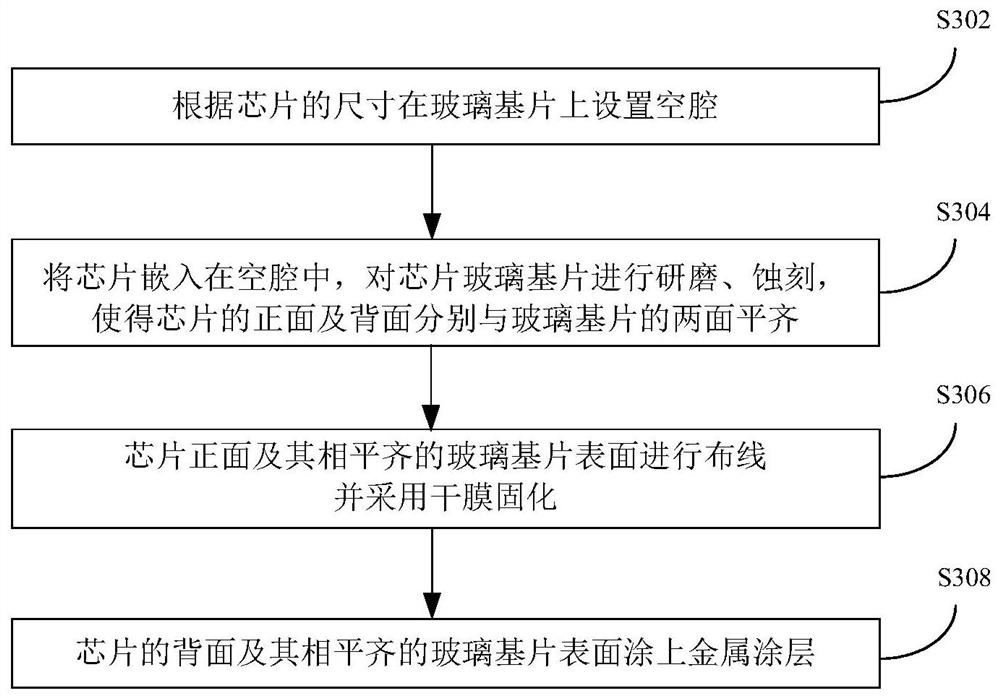

[0073] The chip packaging method provided in this embodiment has the following process steps:

[0074] Preparing the glass substrate (Glass wafer);

[0075] S101, according to the size of the chip to be packaged, perform cavity etching on the surface of the glass substrate (Glass wafer) to form a cavity, see Figure 5 ,details as follows:

[0076] On the surface of the glass substrate (Glass wafer), cover the photoresist, perform exposure and development, retain the cavity area, and then perform dry etching to complete the cavity etching and remove the surface photoresist.

[0077] S102, embedding the chip with the adhesive in the cavity. see Image 6 ,Specific steps:

[0078] Grind the chip wafer to the target thickness. Before cutting the wafer (glass substrate or chip wafer), stick an adhesive film on the back of the chip wafer. After cutting, each chip has an adhesive on the back. The chips are placed in the cavity one by one by pick up and glued and fixed.

[0079] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com