In-memory sparse matrix multiplication operation method, equation solving method and solver

A technology of sparse matrix and multiplication, which is applied in the field of analog circuits, can solve the problems of increased calculation errors, storage errors, waste of storage space, etc., and achieve the effects of reducing calculation errors, reducing storage space, and reducing circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

[0046] For ease of understanding, the structural framework of the in-memory sparse equation solver is firstly introduced.

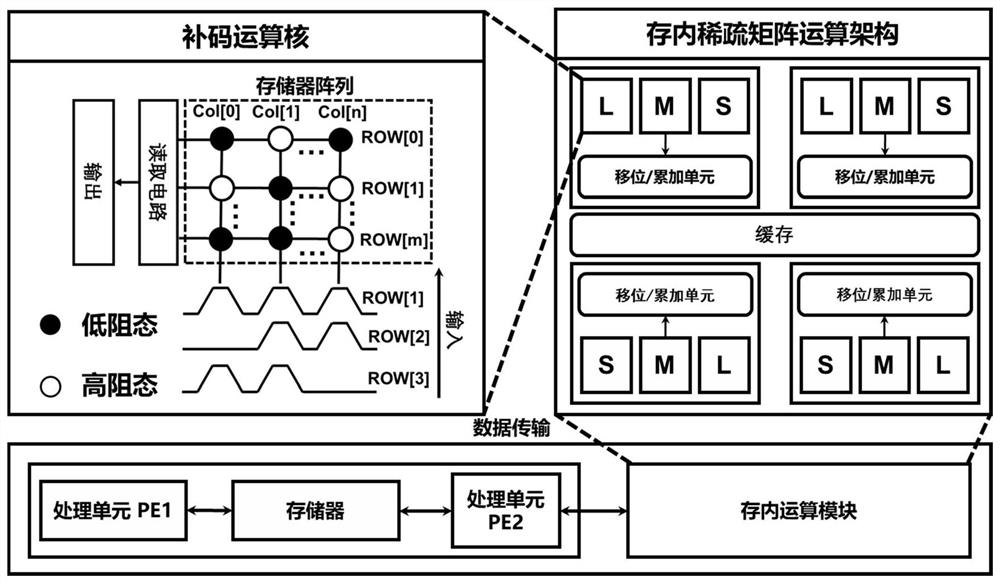

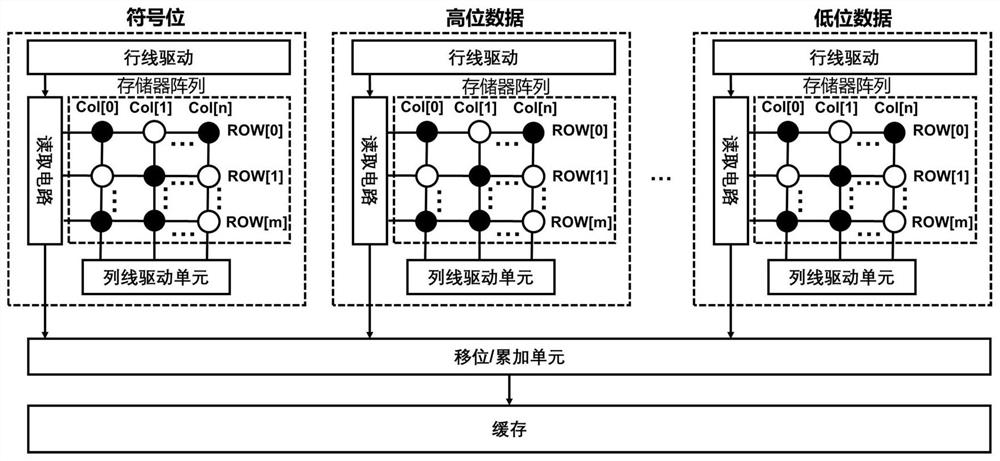

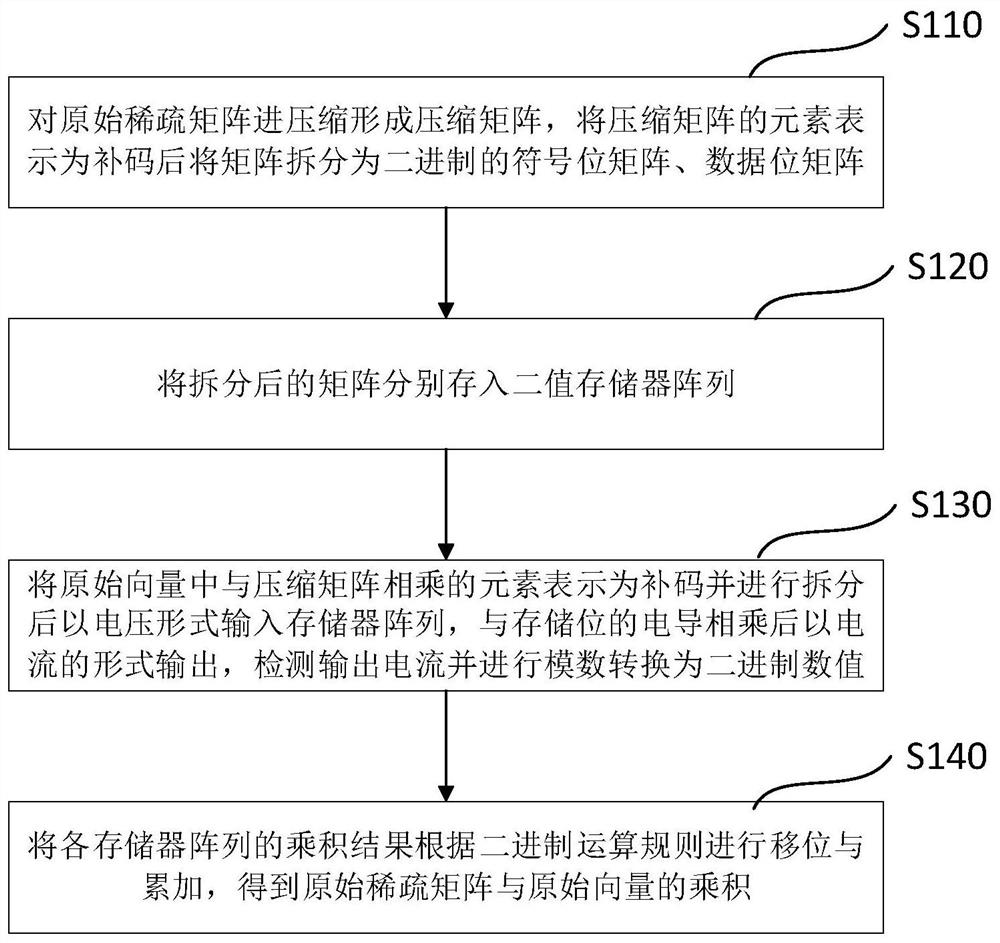

[0047] Such as figure 1 Shown is a schematic structural diagram of an in-memory sparse matrix equation solver in an embodiment of the present invention. The in-memory sparse matrix equation solver includes a digital computing module and an in-memory computing module, where...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com