Silicon carbide-based gallium nitride micron wire array photoelectric detector and preparation method thereof

A photodetector, silicon carbide-based technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of slow development of micro-nano gallium nitride detectors, low device crystal quality, large body surface area, etc., to increase photoelectricity The effect of contact area, long detection range and simple device structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

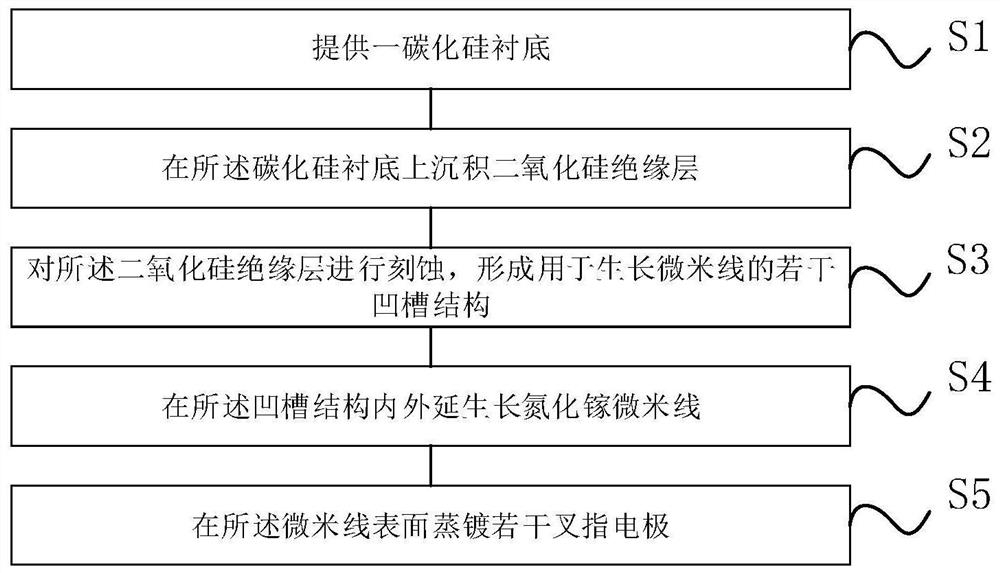

[0043] See figure 1 , figure 1 It is a silicon carbide-based gallium nitride micron line array photodetector provided by an embodiment of the present invention, including:

[0044] S1. Provide a silicon substrate. Specifically, the present embodiment adopts a 2-inch intrinsic type silicon wafer as a substrate, and the silicon substrate is a high-resistance silicon wafer (resistivity > 10 6 Ω·cm), the crystal orientation of the silicon wafer is .

[0045] S2. Deposit a silicon dioxide insulating layer on the silicon carbide substrate; in this embodiment, a 2.5-4 μm silicon dioxide insulating layer can be formed on the surface of a 2-inch silicon wafer by a thermal reduction method.

[0046] S3. Etching the silicon dioxide insulating layer to form several groove structures for growing micron wires, wherein the width of the groove structure is 8-12 μm, and the depth of the groove structure is 3.5 to 4.5 μm. The spacing between the groove structures is 8-10 μm;

[0047] Concre...

Embodiment 2

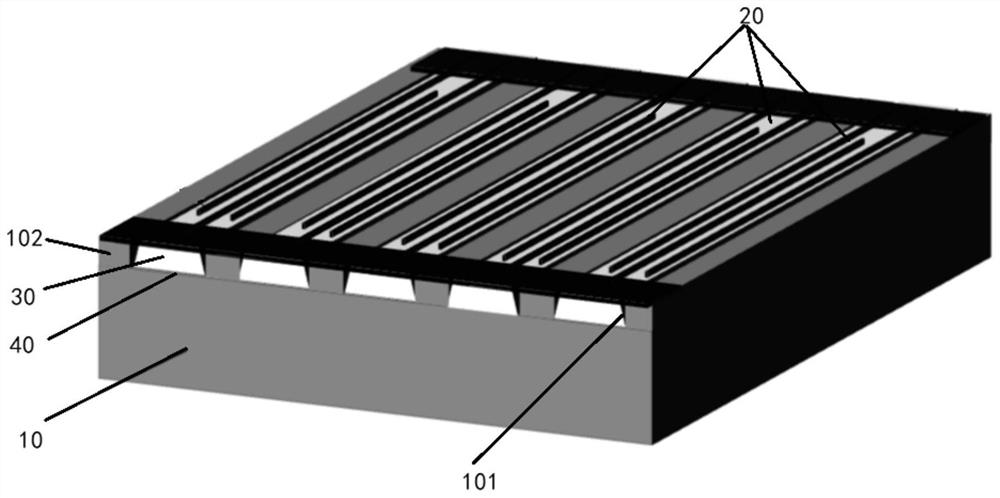

[0057] See Figure 2-Figure 6 , the silicon carbide-based gallium nitride micron line array photodetector of this embodiment can be prepared by the method of embodiment 1, and the device includes:

[0058] silicon carbide substrate 10;

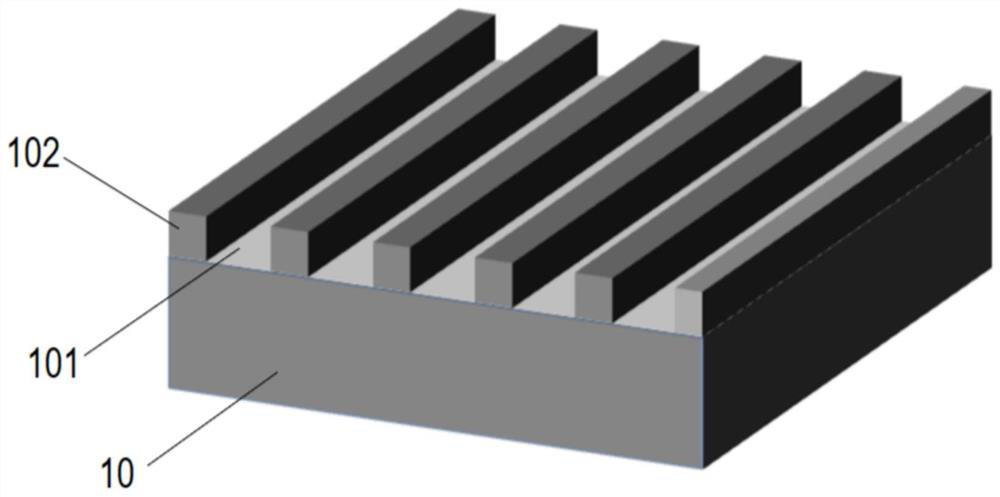

[0059] A silicon dioxide insulating layer 102 is formed at intervals on the silicon carbide substrate 10, so that several groove structures 101 are formed on the substrate not covered with the silicon dioxide insulating layer 102, wherein the resistivity of the insulating layer 102 is greater than 10 16 Ω cm;

[0060] Gallium nitride micro-wires 30 are formed in the groove structure 101, and the extension direction of the gallium nitride micro-wires 30 is consistent with the extending direction of the groove structure 101, wherein there are multiple gallium nitride micro-wires 30 in the form of array shape;

[0061] The aluminum nitride buffer layer 40 is formed inside the gallium nitride micro-wire 30 of the groove structure 101; the alum...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com