Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve the problems of poor control ability of gate structure and difficult channel, so as to alleviate short channel effect, improve electrical performance, reduce short channel Dow effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] It can be seen from the background art that the devices formed so far still have the problem of poor performance. The reasons for the poor performance of the device are analyzed in conjunction with a method of forming a semiconductor structure.

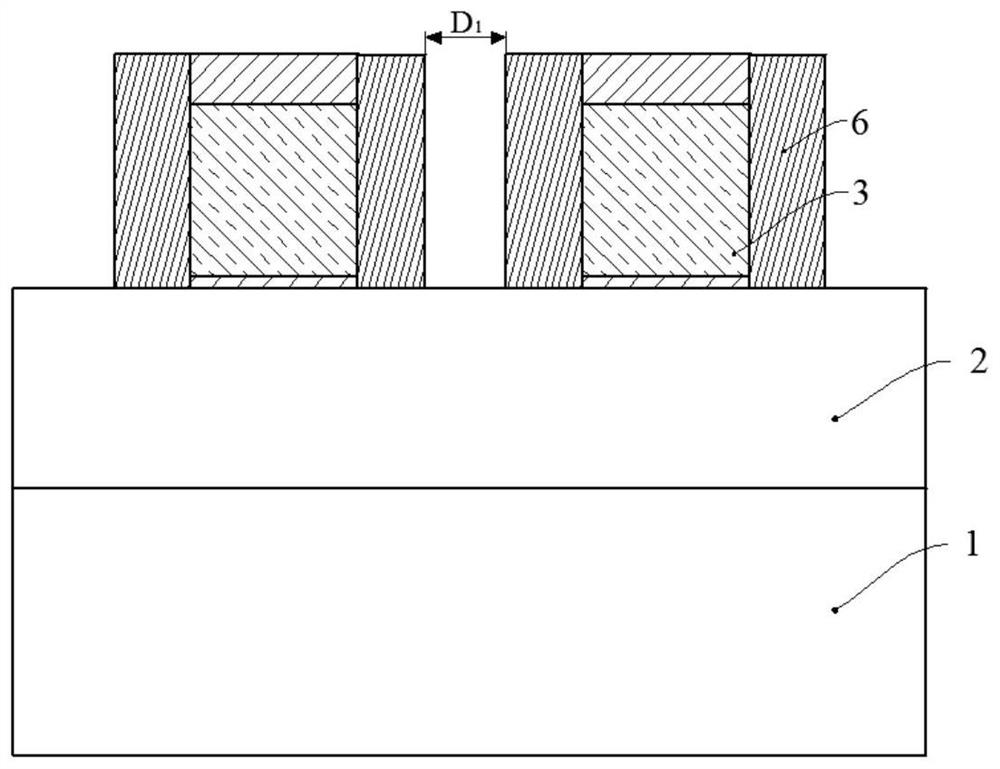

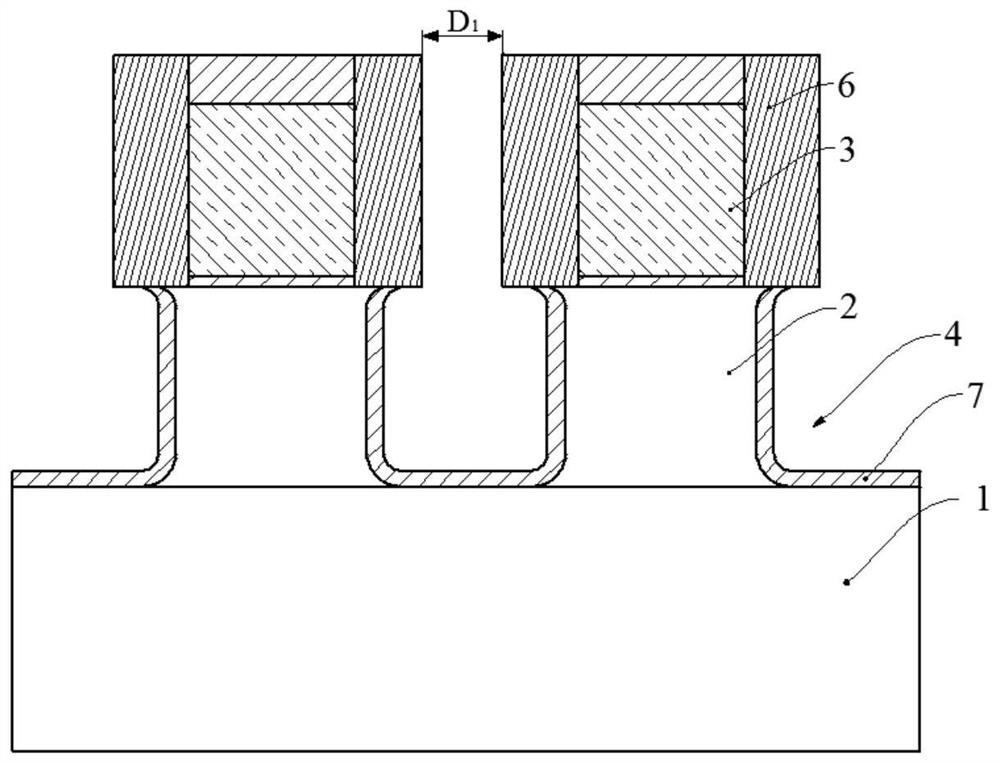

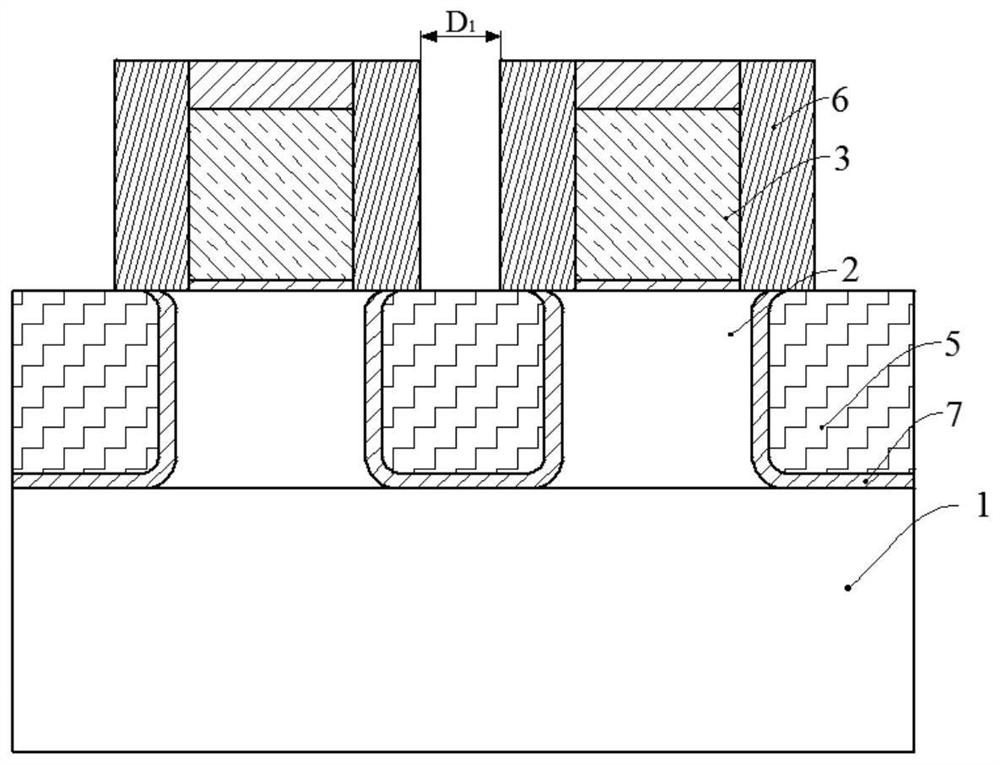

[0030] Figure 1 to Figure 3 A structural schematic diagram corresponding to each step in a method for forming a semiconductor structure is shown.

[0031] like figure 1 As shown, a base is provided, the base includes a substrate 1, a fin 2 on the substrate 1, and a gate structure 3 across the fin 2, and the gate structure 3 covers the fin Part of the top wall and part of the side wall of the part 2; a side wall layer 6 is formed on the side wall of the gate structure 3, and the size between the side wall layers 6 on the side wall of the adjacent gate structure 3 as D 1 .

[0032] like figure 2 As shown, the fins 2 on both sides of the gate structure 3 are etched to form a groove 4 in the fin 2; an anti-diffusion layer 7...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Horizontal size | aaaaa | aaaaa |

| Horizontal size | aaaaa | aaaaa |

| Horizontal size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com