Manufacturing method of MOS (metal oxide semiconductor) transistor

A technology of MOS transistors and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of low junction capacitance and junction leakage performance, inability to meet the requirements, and achieves the reduction of junction capacitance, junction leakage, and reduction. Effects of small short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

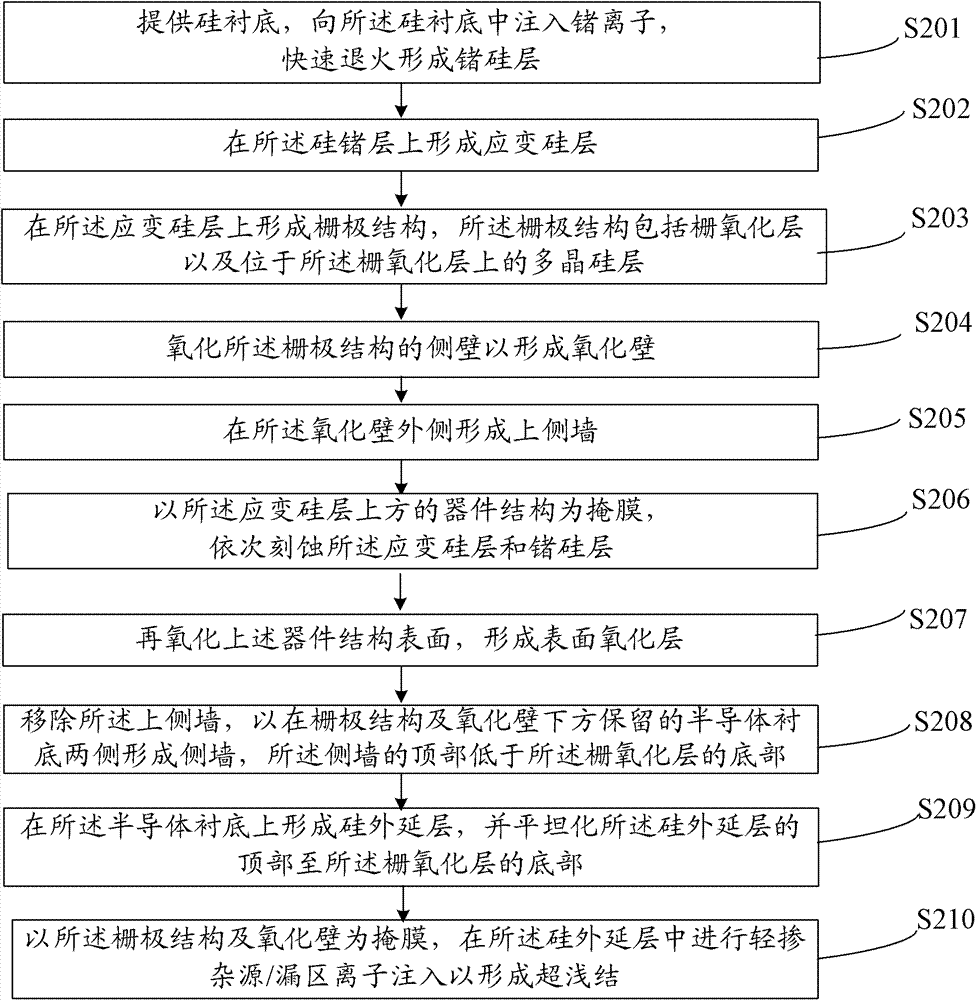

[0043] The present invention proposes a kind of manufacturing method of MOS transistor, and this method comprises the following steps:

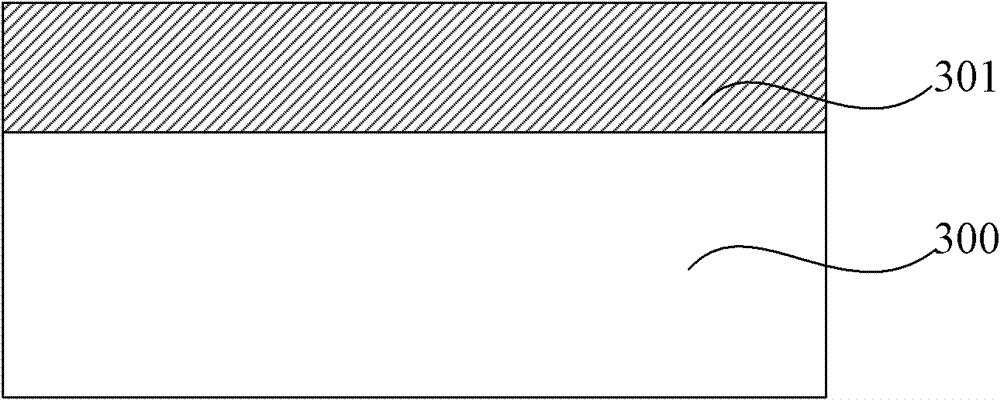

[0044] Provide semiconductor substrates;

[0045] forming a gate structure on the semiconductor substrate, the gate structure comprising a gate oxide layer and a polysilicon layer on the gate oxide layer;

[0046] oxidizing sidewalls of the gate structure to form oxide walls;

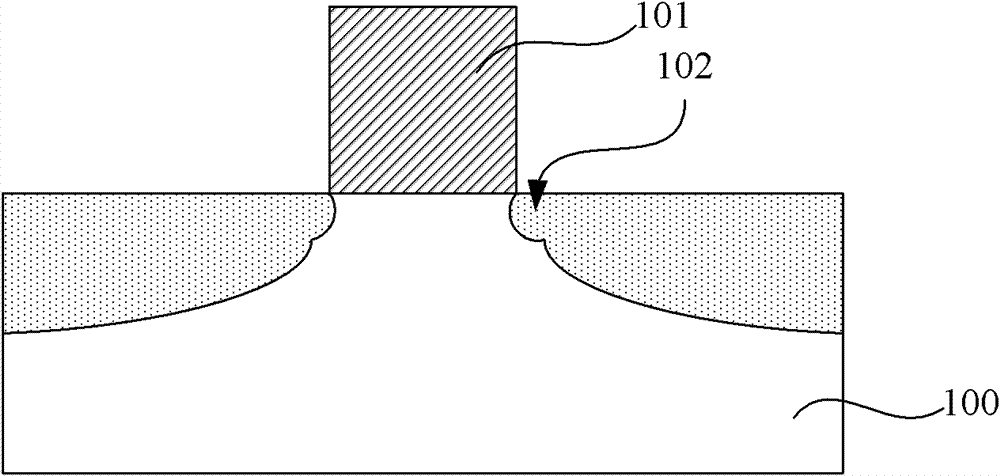

[0047] using the gate structure and the oxide wall as a mask to remove part of the semiconductor substrate;

[0048] re-oxidizing the remaining upper surface of the semiconductor substrate to form a surface oxide layer;

[0049] Etching the surface oxide layer to form sidewalls on both sides of the semiconductor substrate remaining under the gate structure and the oxide wall, the top of the sidewalls is lower than the bottom of the gate oxide layer;

[0050] forming a silicon epitaxial layer on the semiconductor substrate, and planarizing the top of the silicon epit...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Feature size | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com