Low-delay semi-dynamic trigger based on tunneling field effect transistor hybrid integration

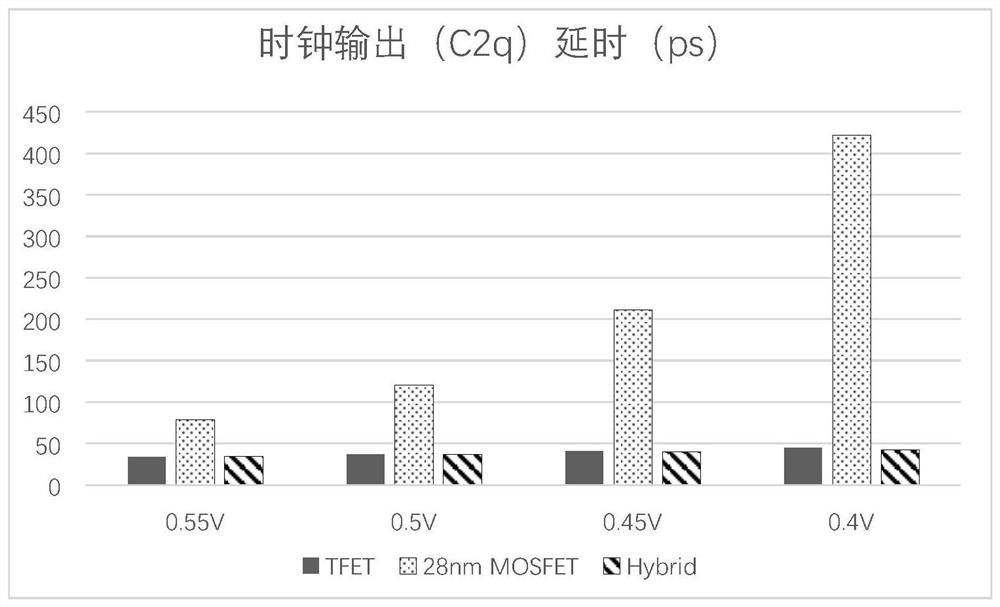

A technology of semi-dynamic trigger and tunneling field effect, which is applied in the direction of pulse generation, electrical components, and electric pulse generation. It can solve the problems of increasing circuit switching activity and increasing dynamic power consumption, so as to improve frequency performance and reduce dynamic switching. The effect of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

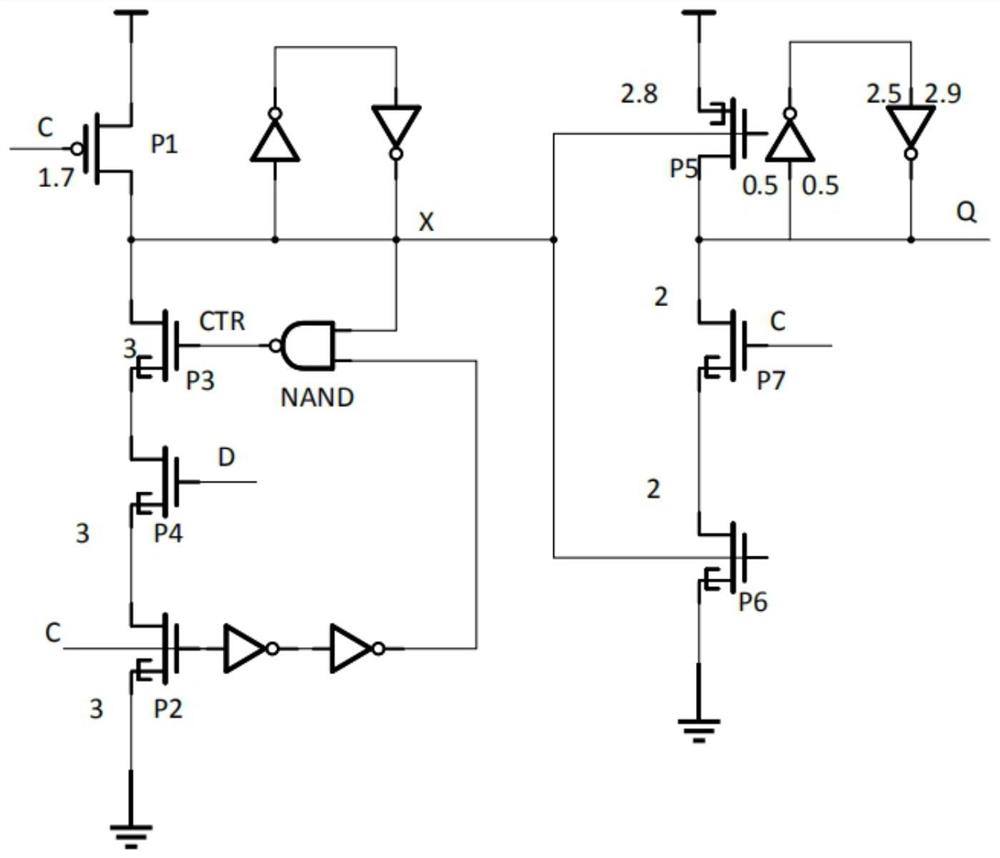

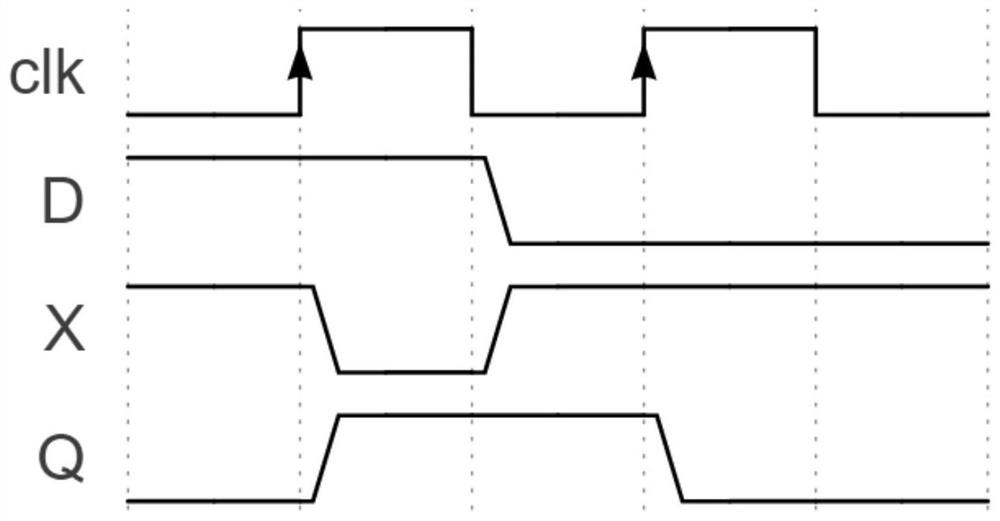

[0025] The present invention is based on a low-delay semi-dynamic flip-flop integrated with tunneling field effect transistors. The flip-flop uses TFETs to replace MOSFETs and CMOS logic gates in the critical path of the circuit. and a static backend for latching and outputting data. The dynamic front-end circuit consists of a pull-up circuit, a pull-down circuit and a latch. The pull-up circuit is a P-type MOSFET, and the pull-down circuit uses three N-type TFET transistors, two A TFET inverter and a TFET NAND gate replace the original MOSFET and CMOS logic gate; the static output circuit uses a pull-up P-type TFET and two pull-down N-type TFET transistors to replace the original MOSFET, followed by a CMOS latch. in:

[0026] The four transistors in the front-end dynamic circuit are the first pull-up transistor P1, the first pull-down transistor P2, the discharge transistor P3 and the data input transistor P4, the first pull-up transistor P1 is a P-MOSFET, and its gate is con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com