Schmitt trigger based on GaAs HEMT process

A Schmitt trigger and process technology, applied in the direction of pulse generation, electrical components, and electric pulse generation, to achieve the effects of strong anti-interference and anti-radiation capabilities, small transmission delay, and fast switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

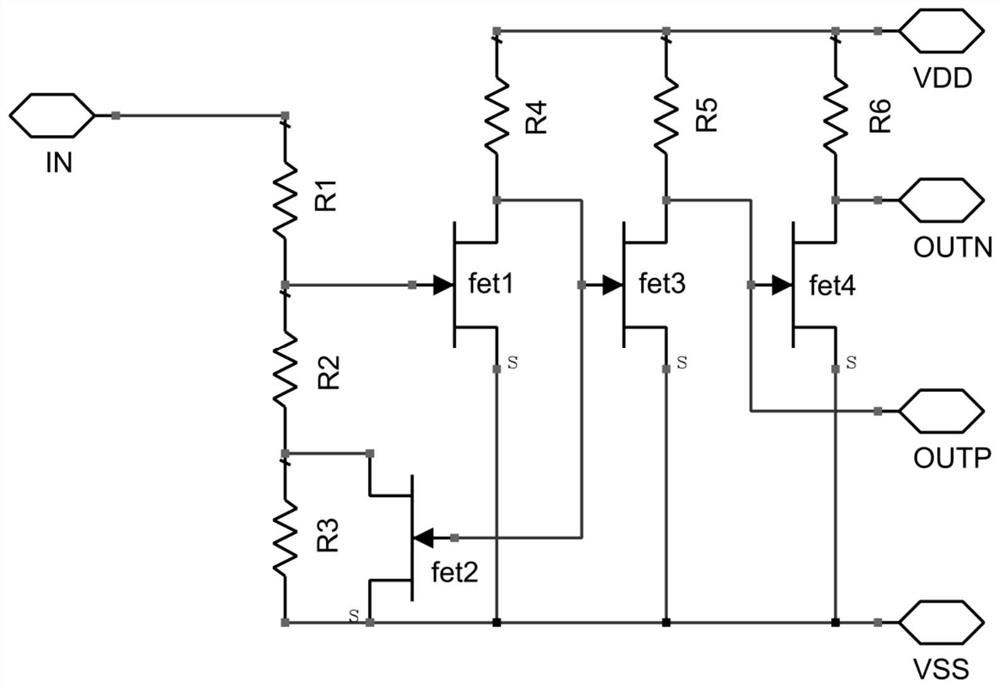

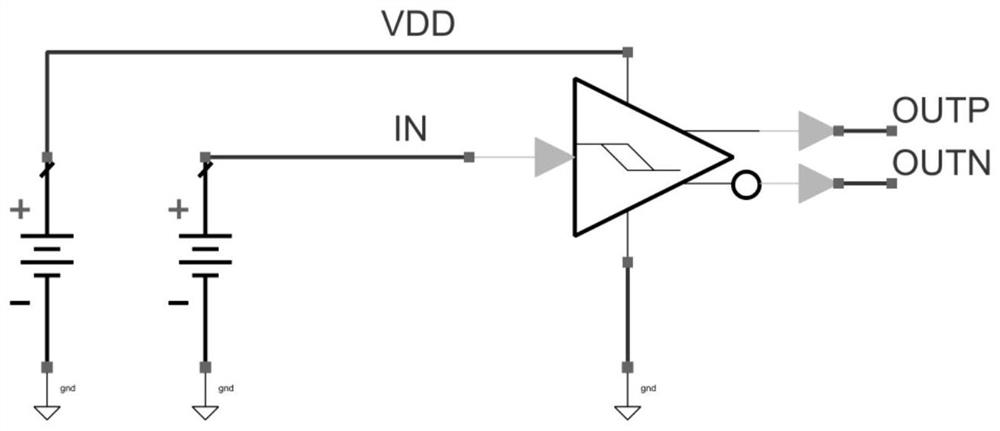

[0022] Embodiment 1: as figure 1 As shown, its circuit structure is specifically: a Schmitt trigger based on GaAs HEMT technology, including field effect transistors fet1, fet2, fet3, and fet4, and field effect transistors fet1, fet2, fet3, and fet4 are all made of GaAs materials. The formed transistor is an enhancement type field effect transistor.

[0023] The Schmitt trigger has an input terminal IN, a positive power supply terminal VDD, a negative power supply terminal VSS, an output non-inverting terminal OUTP, and an output inverting terminal OUTN. The input terminal IN is connected to a resistor R1, and the other end of the resistor R is connected in series with resistors R2 and R3. Then connect the negative terminal VSS of the power supply, the lead terminal between the resistor R1 and the resistor R2 is connected to the gate of the fet1, the drain of the fet1 is connected to the positive terminal VDD of the power supply through the resistor R4; Connect the drain of f...

Embodiment 2

[0032] Embodiment 2: as Figure 4 As shown, the Schmitt trigger in this embodiment is improved on the basis of Embodiment 1. A diode is connected in series between the input terminal IN of the Schmitt trigger in the embodiment and the resistor R1 for voltage reduction, and the input A diode d1 for step-down is connected in series between the terminal IN and the resistor R1. The diode d1 is a single diode or a plurality of diode groups connected in series.

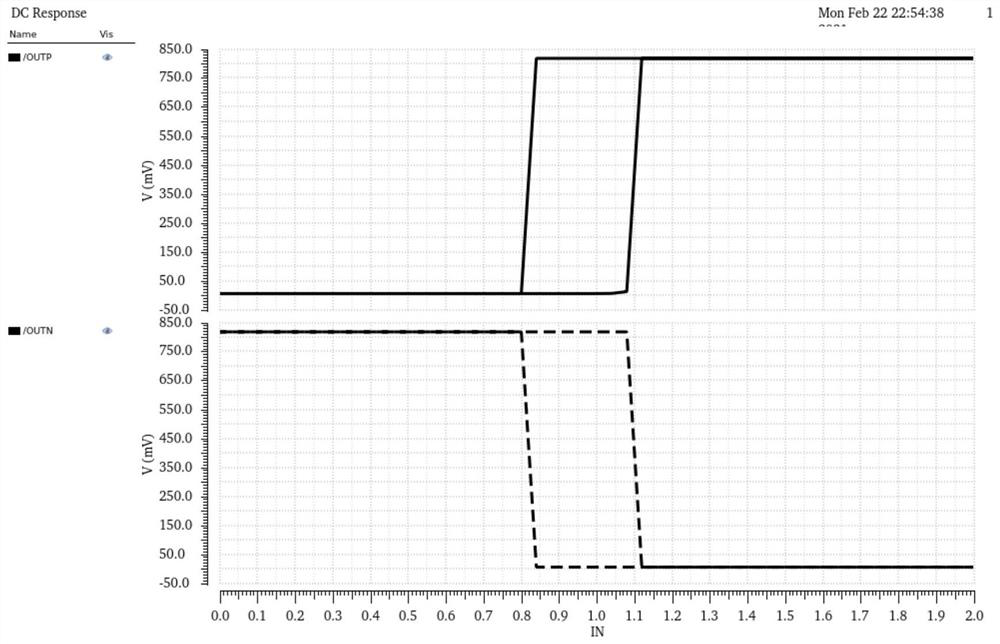

[0033] For some applications with higher voltage (such as 5V-TTL), you can directly divide the voltage with resistors according to the above figure, or you can add diode d1 to step down the voltage as shown in the figure below, and adjust the input logic level threshold to 2V ~ 3V, hysteresis voltage 1V. Although only one diode is shown in the figure, if VSS is powered by a negative voltage, that is, the IN-VSS voltage difference is large, the number of series diodes can be increased to achieve a larger range of level shi...

Embodiment 3

[0034] Embodiment 3: This embodiment is an improvement on the basis of Embodiment 1 or 2, and is mainly applicable to scenarios where low power consumption is required for the Schmitt trigger or the voltage of the power supply VDD-VSS is very high. If the circuit pair requires low power consumption, or the VDD-VSS voltage is very high, the pull-up resistors R4, R5, and R6 need to be large, which will inevitably increase the circuit area. Therefore, D-mode transistors can be used to add resistors to form a constant current. source to limit the operating current while reducing the circuit area. The specific circuit principles include: on the basis of embodiment 1 or 2, adding depletion type field effect transistors dfet1, dfet2, dfet3, such as Figure 5 As shown, dfet1 is set in series between resistor R4 and VDD; dfet2 is set in series between resistor R5 and VDD; dfet3 is set in series between resistor R6 and VDD; VDD is respectively connected to the drain of dfet1, the drain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com