Ring polynomial multiplier circuit in lattice password encryption and decryption

A technology of polynomial multiplication and lattice cipher, applied in the field of hardware implementation of lattice cipher, which can solve problems such as consuming a large time period and resources, and not being so easy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

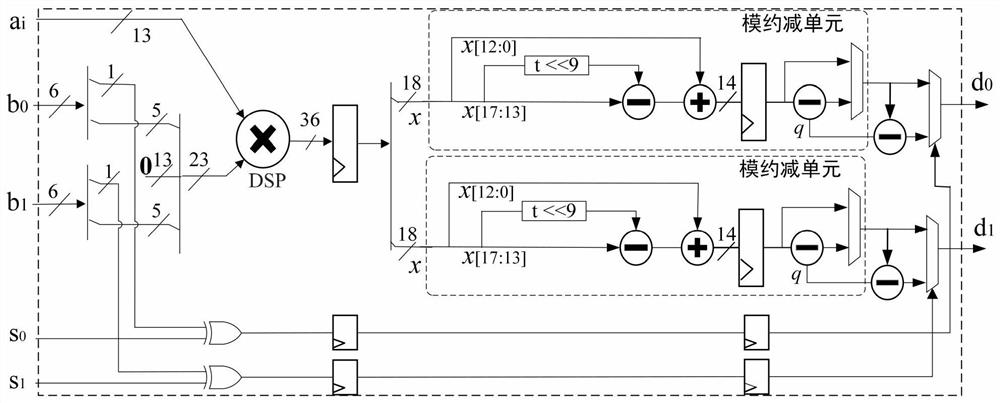

Embodiment Construction

[0025] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings.

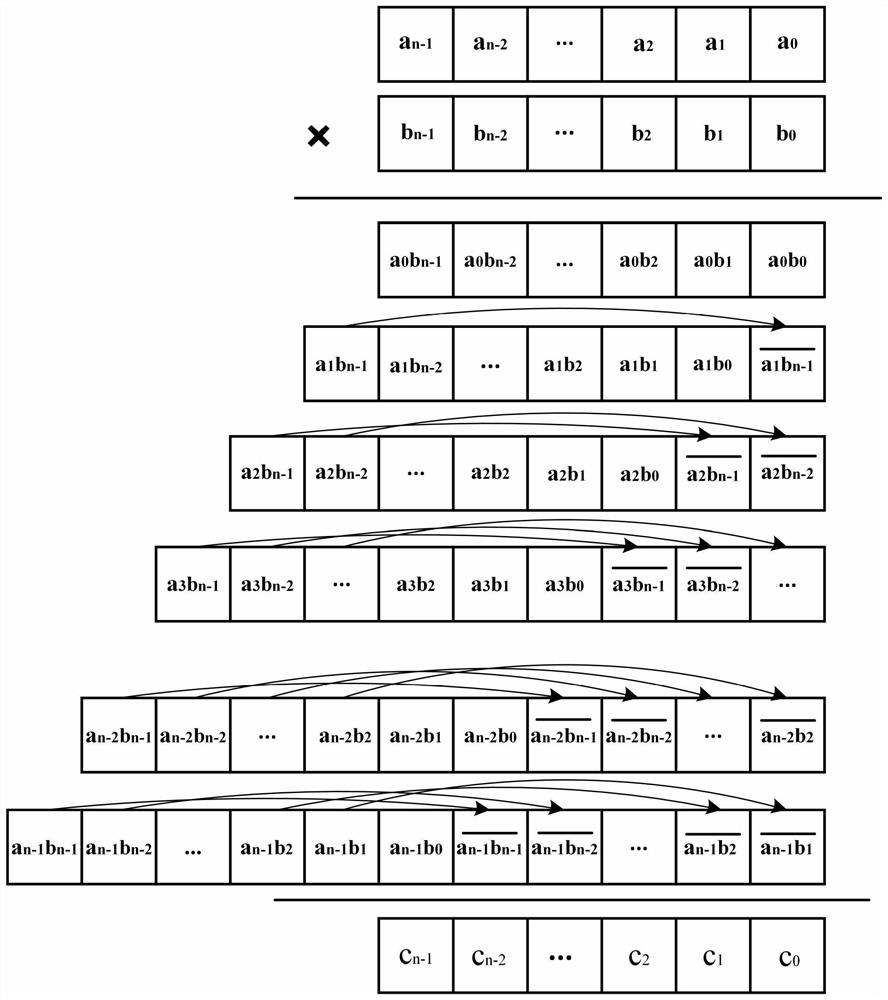

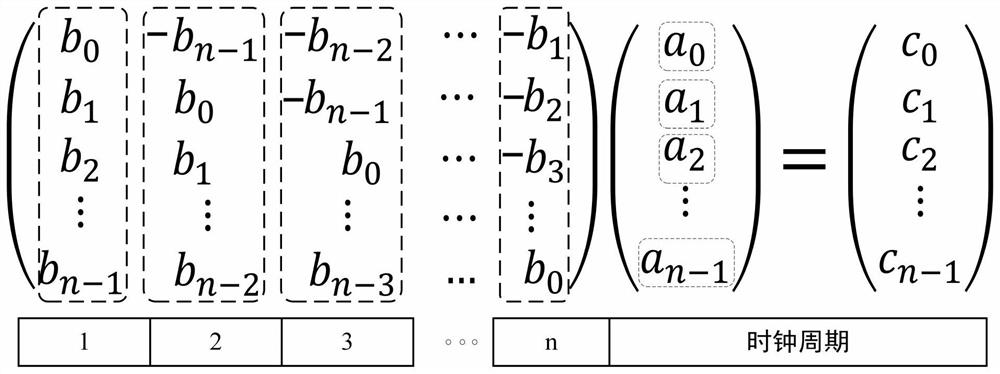

[0026] For the SPM algorithm, most of the designs are focused on lightweight, that is, for a single or a small number of modular multiplication units according to the following ring polynomial calculation formula:

[0027]

[0028] Continuously reuse a single multiplier unit to calculate the final polynomial coefficients in turn. In addition to the shortcomings of excessive time consumption, this method also has slow data processing speed, that is, low throughput rate, and complex control units when implemented in hardware circuits. The circuit structure of SPM needs multiple modular multiplication units to calculate in parallel in order to obtain higher throughput. In order to understand the calculation process of the integer ring polynomial Schoolbook algorithm more clearly, figure 1 The calculation of the whole algorithm is expanded ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com