FPGA one-dimensional signal recognition neural network acceleration method based on opencl

A neural network and signal recognition technology, applied in the field of acceleration of convolutional neural networks, can solve problems such as system performance degradation, achieve large data throughput, increase computing speed, and achieve the effect of high-performance parallel computing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The specific embodiments of the present invention will be described in further detail below with reference to the accompanying drawings and specific embodiments.

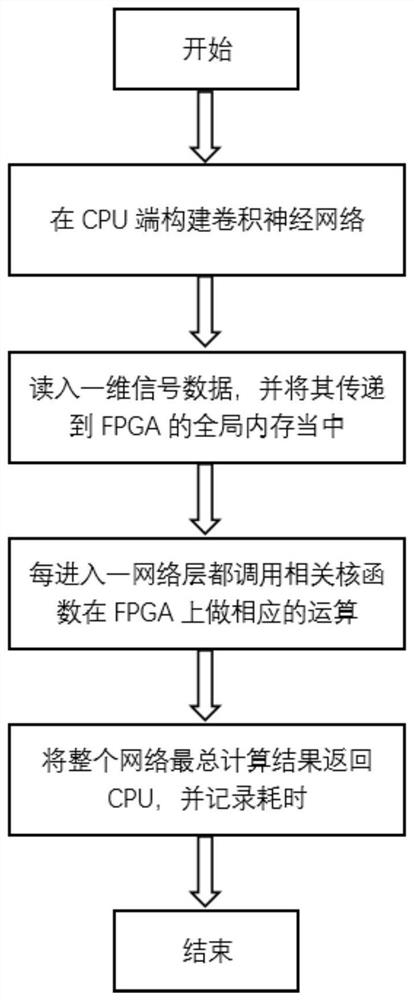

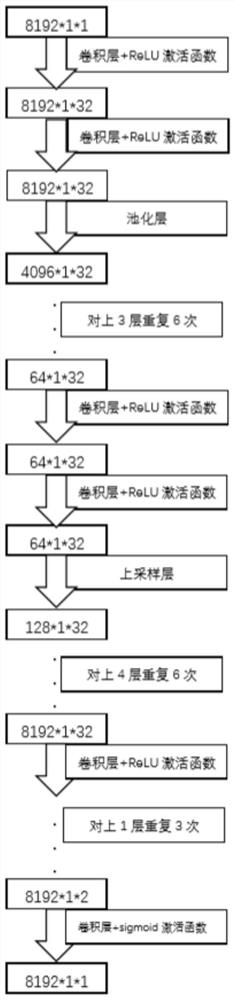

[0021] like Figures 1 to 2 As shown, the FPGA one-dimensional signal recognition neural network acceleration method based on OpenCL specifically includes the following steps:

[0022] 1) Build a one-dimensional convolutional neural network on the CPU host side;

[0023] 2) Read the one-dimensional signal data with a size of 8192*1 and the weight and bias data for convolution of the signal data obtained by training into the host memory from the text file;

[0024] 3) Calculate the first convolutional layer of the convolutional neural network:

[0025] 3a) the signal data obtained after the edge expansion processing of the signal data in step 2), and the weight and bias data used by the convolution layer are read into the FPGA global memory;

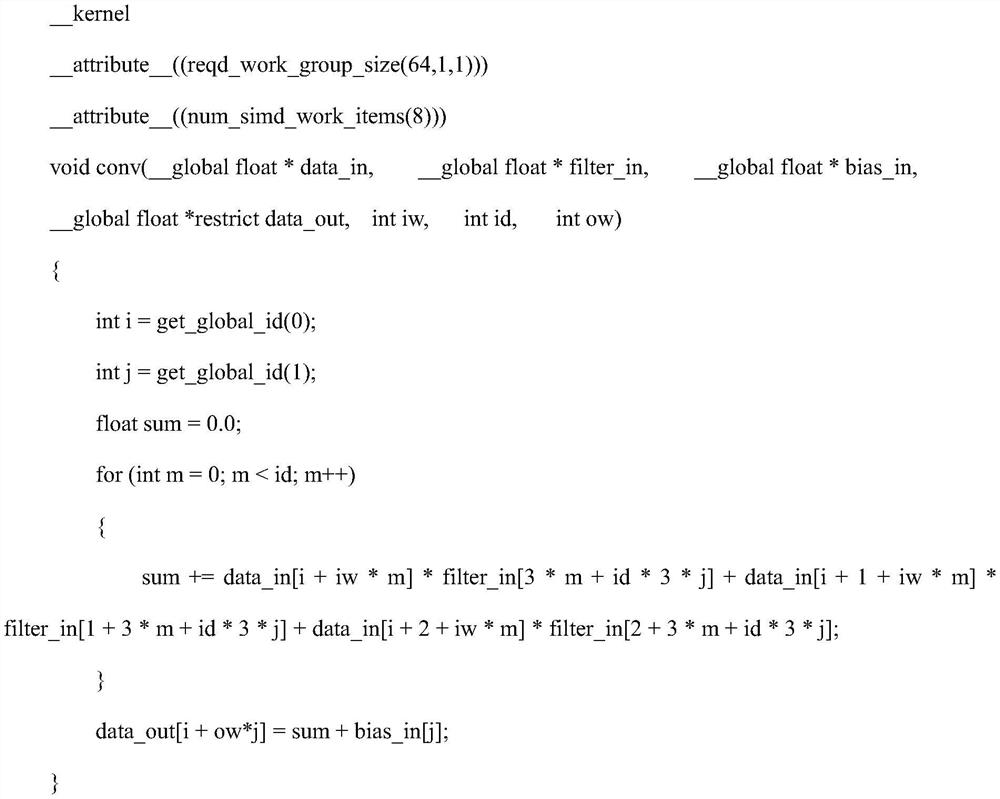

[0026] 3b) Call the convolution kernel function to operate the d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com