Composite substrate and preparation method thereof and electronic component

A technology of electronic components and composite substrates, applied in the direction of electrical components, impedance networks, etc., can solve problems such as radio frequency loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

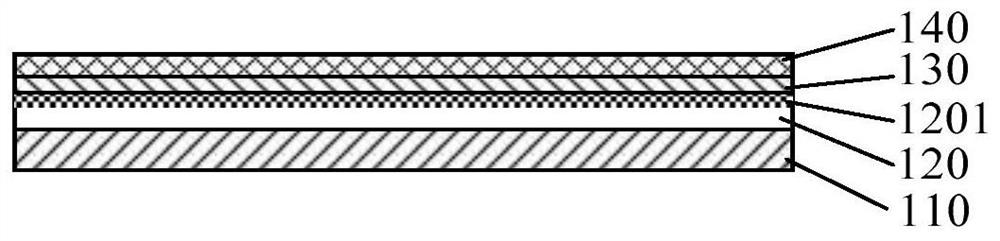

[0058] Specifically, refer to Figure 5 , the preparation method comprises:

[0059] S11 , prepare the substrate layer 110 .

[0060] This step also includes performing semiconductor-grade RCA cleaning on the substrate layer 110 to obtain a clean surface.

[0061] S12, preparing a microcrystalline layer 100 on the substrate layer.

[0062] Optionally, this step can be obtained by the following methods:

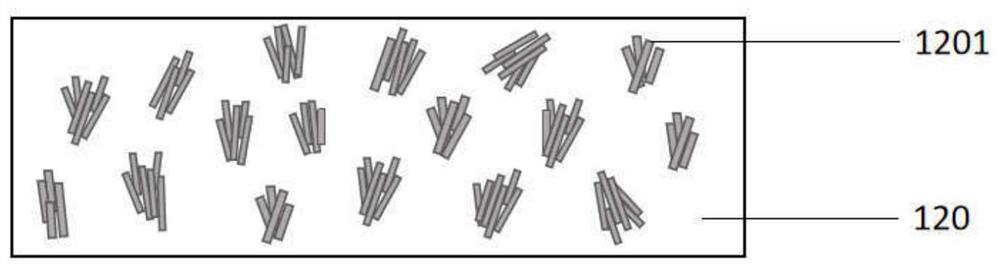

[0063] Under silicon-containing gas or a mixture of silicon-containing gas and other gases, or under germanium-containing gas or a mixture of germanium-containing gas and other gases, microcrystalline grains containing random crystal orientations are grown on the substrate layer 110 The microcrystalline layer 100.

[0064] That is to say, in this step, the substrate in step S11 can be placed in a deposition furnace, and a silicon-containing gas or a mixture of silicon-containing gas and other gases, such as SiH 4 The gas is used to control the growth process conditions to...

Embodiment 1

[0087] 1) Provide a single crystal silicon substrate layer.

[0088] 2) Perform semiconductor-grade RCA cleaning on the single crystal silicon substrate layer to obtain a clean surface.

[0089] 3) Place the monocrystalline silicon substrate layer in step 2) in the deposition furnace, and pass through the SiH-containing 4 The gas is used to control the growth process conditions to grow a microcrystalline silicon layer containing microcrystalline grains arranged in random crystal directions, and the distance between microcrystalline grains in the microcrystalline silicon layer is controlled at about 300nm.

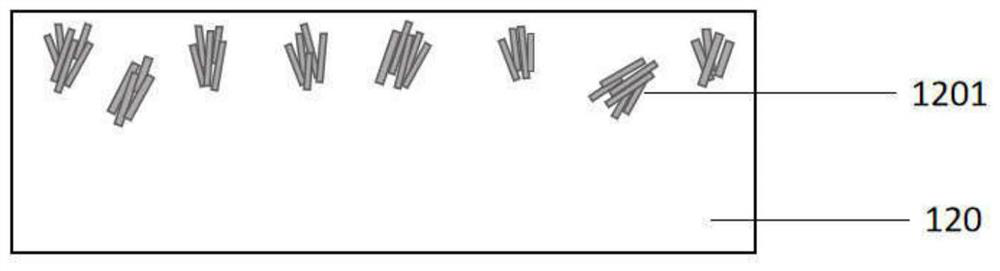

[0090] 4) Annealing the microcrystalline silicon layer in step 3) at 800° C. for 5 hours to form a polycrystalline silicon layer with crystal grain clusters with a size of 100 nm to 500 nm.

[0091] 5) An insulating layer is formed on the polysilicon layer obtained in step 4).

[0092] 6) Polishing the insulating layer in step 5) to obtain a smooth surface.

[0093] 7) P...

Embodiment 2

[0095] 1) Provide a single crystal silicon substrate layer.

[0096] 2) Perform semiconductor-grade RCA cleaning on the single crystal silicon substrate layer to obtain a clean surface.

[0097] 3) Place the monocrystalline silicon substrate layer in step 2) in the deposition furnace, and pass through the SiH-containing 4 The gas is used to control the growth process conditions to grow a microcrystalline silicon layer containing microcrystalline grains arranged in random crystal directions, and the distance between microcrystalline grains in the microcrystalline silicon layer is controlled at about 1000nm.

[0098] 4) Annealing the microcrystalline silicon layer in step 3) at 950° C. for 10 h to form a polycrystalline silicon layer with crystal grain clusters with a size of 500 nm to 1000 nm.

[0099] 5) An insulating layer is formed on the polysilicon layer obtained in step 4).

[0100] 6) Polishing the insulating layer in step 5) to obtain a smooth surface.

[0101] 7) A ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| grain size | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com