Optimization method of system-in-package structure

A system-level packaging and optimization method technology, applied in the field of microelectronics, can solve the problems of complex operation, high cost, high equipment and process requirements, etc., to avoid random errors, reduce the required time, and reduce costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

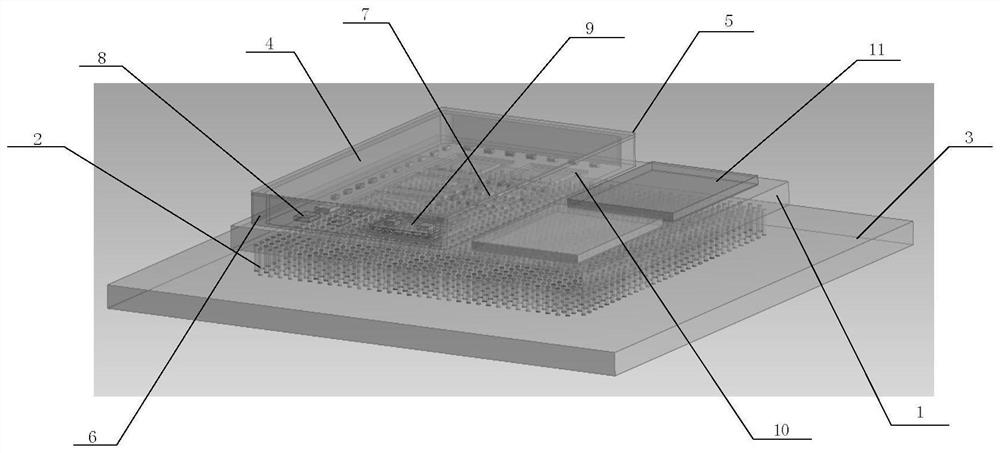

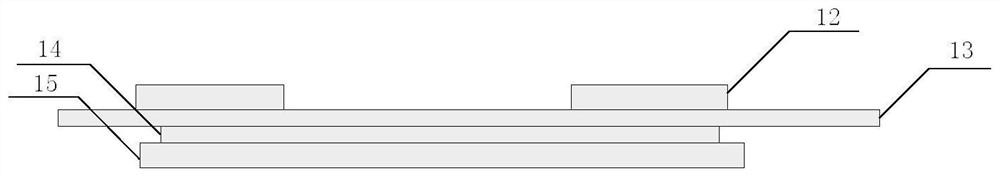

[0030] refer to figure 1 with figure 2 , The existing system-level package SIP structure is composed of low-temperature co-fired ceramic LTCC, ceramic solder column array CCGA, kovar frame, passive components, bare chips, and chip stacks. It is a low-temperature co-fired ceramic LTCC welded on the bottom surface of the ceramic welding column array CCGA. On the LTCC, passive components, bare chips, and chip stacks are assembled together, and a metal partition wall is used to construct a hermetic packaging area as a whole.

[0031] The specific SIP structure used in this example is to use low-temperature co-fired ceramics as the substrate 1, weld the ceramic welding column array 2 on the bottom surface of the substrate, and weld the other side of the ceramic welding column array with the printed circuit board 3, and the upper surface of the substrate is equipped with a Cutting frame 4 and cover plate 5, there is a gap between the boundary of the cutting frame and the substrate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com