Alignment pattern, semiconductor structure with alignment pattern and manufacturing method of semiconductor structure

A technology for aligning patterns and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, and photoengraving processes of patterned surfaces. It can solve problems such as poor quasi-quality and achieve area reduction, area reduction, and elimination The effect of the etch loading effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] It can be seen from the background art that the accuracy of alignment using existing alignment patterns needs to be improved.

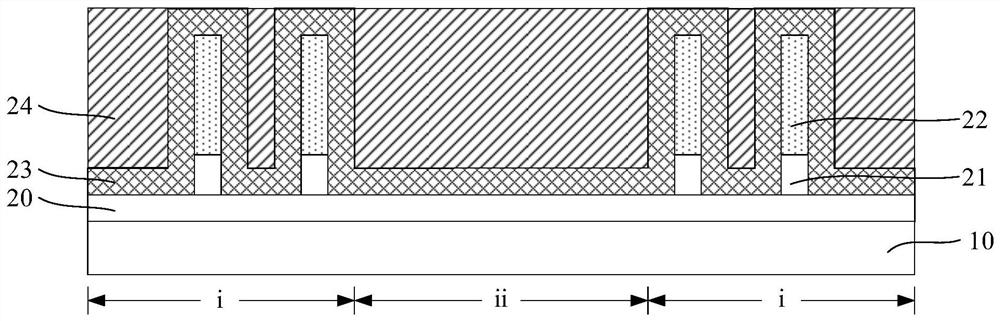

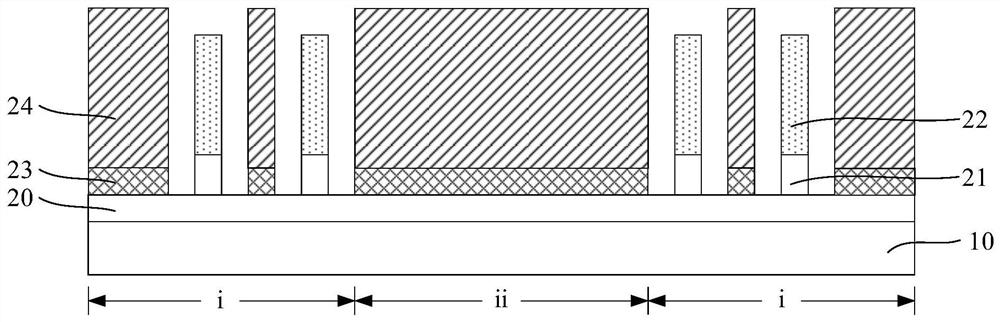

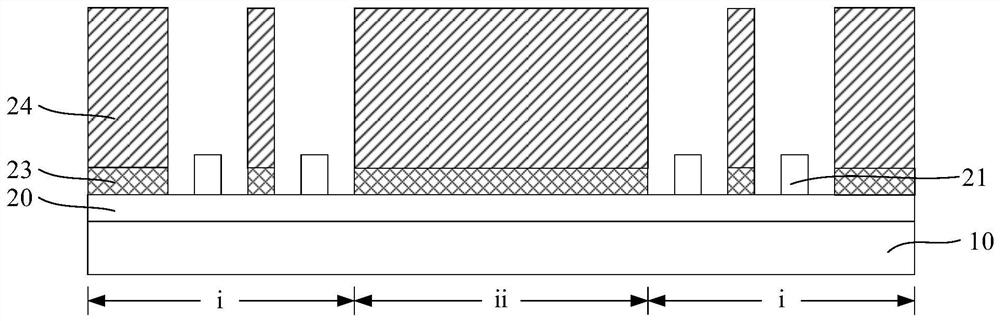

[0028] Figure 1 to Figure 4 It is a structural schematic diagram corresponding to each step of a method for forming a semiconductor structure with aligned patterns.

[0029] refer to figure 1 , providing a substrate comprising a first region i and a second region ii located between adjacent first regions i, the substrate comprising a substrate 10 and a polysilicon layer 20 located on the surface of the substrate 10, the surface of the substrate of the first region i is formed with discrete The first dielectric layer 21 has a photoresist layer 22 on the top surface of the first dielectric layer 21; a second dielectric layer 23 is also formed on the surface of the base, and the second dielectric layer 23 also covers the top and sidewalls of the photoresist layer 22. The thickness of the second dielectric layer 23 is smaller than that of the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com