Reconfigurable field effect transistor with structure of asymmetric sidewalls and vertically stacked channels

A technology of field effect transistors and vertical stacking, which is applied in the direction of transistors, semiconductor devices, electrical components, etc., and can solve the problems of low on-state drive current, shortened transistor switching time, and high process development costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

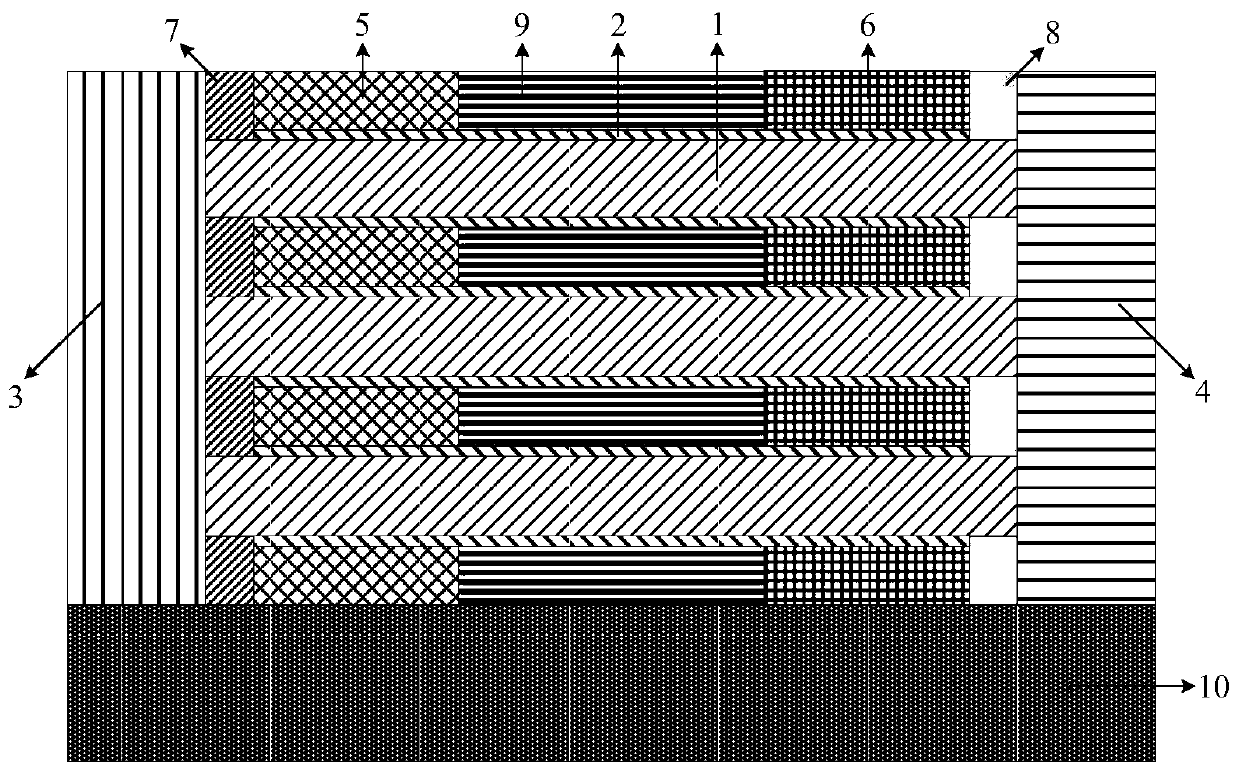

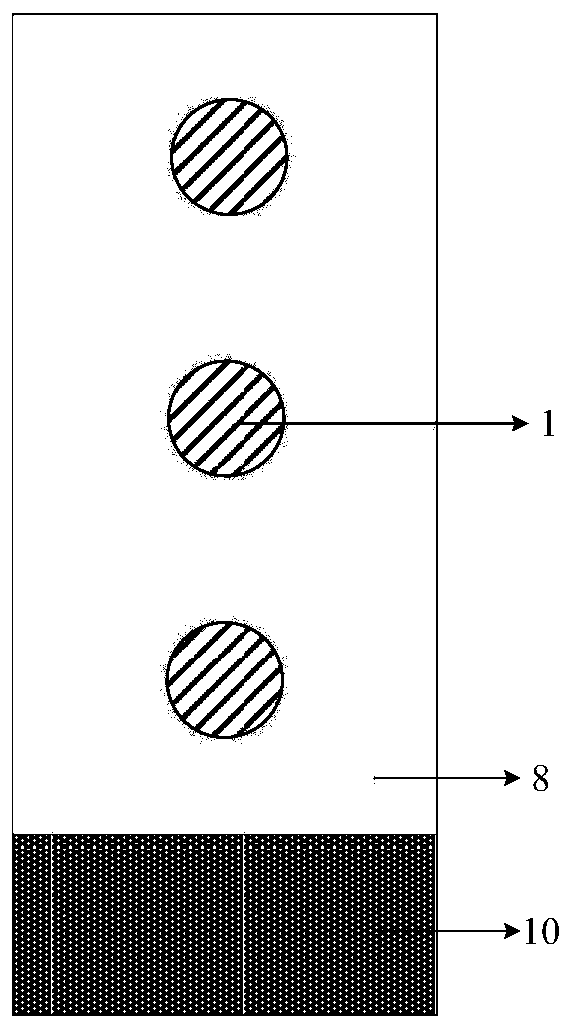

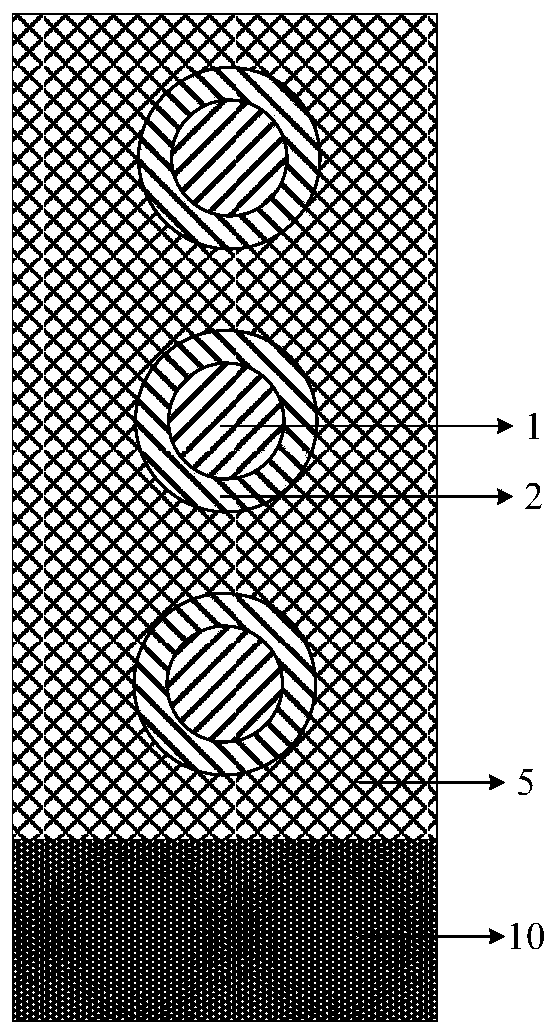

[0029] refer to Figure 1-4 , the reconfigurable field effect transistor with asymmetrical sidewall and vertically stacked channel structure, its asymmetric feature lies in the sidewall 7 on the source side between the source 3 and the control gate 5 and the drain 4 and the pole The materials used for the side wall 8 on the drain side between the permanent gates 6 are different, and the length of the side wall 7 on the source side is less than or equal to the length of the side wall 8 on the drain side; Stacking in a direction perpendicular to the substrate 10, the number of times of stacking is greater than or equal to two times.

[0030] A reconfigurable field effect transistor with an asymmetrical sidewall and vertically stacked channel structure, its structural features include multiple vertically stacked channels 1, gate oxides 2 wrapped outside...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com