FPGA parallel acceleration system based on CNN image quality enhancement algorithm

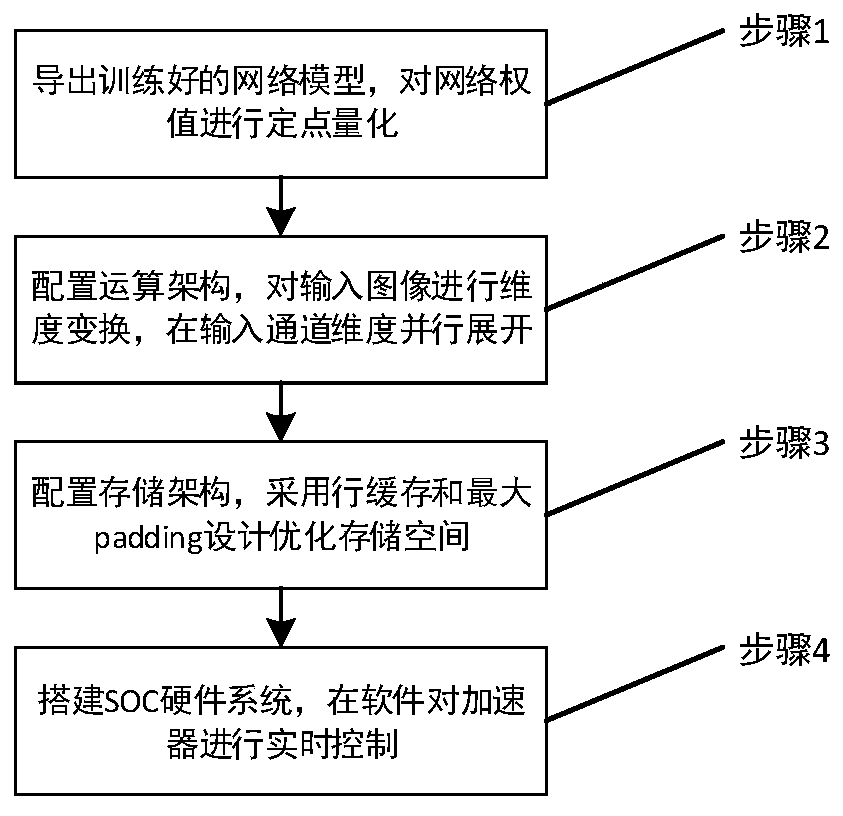

A technology that enhances algorithms and accelerates systems, and is used in concurrent instruction execution, computing, neural learning methods, etc. to reduce power consumption, achieve computing efficiency, and meet the needs of video and image applications.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Embodiments of the present invention will be described below in conjunction with the accompanying drawings.

[0036] Such asfigure 1 As shown, the present invention designs a kind of FPGA parallel acceleration system based on the picture quality enhancement algorithm of CNN, mainly comprises: CPU, DMA controller, bus module, accelerator IP core module, on-chip memory BRAM, off-chip memory SDRAM. The main design considerations for each module are as follows:

[0037] The central processing unit is mainly used to control the system operation process in this system, including controlling the start and stop of the accelerator, configuring the accelerator, processing accelerator interrupts, and controlling the DMA to complete data transfer.

[0038] The accelerator IP core module, the core computing system of the present invention, is designed on the basis of the third point above, and is mainly composed of LUT and DSP resources inside the FPGA. During calculation, each cal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com