Method for improving spacer shape

An isolation sidewall and isolation sidewall etching technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as poly damage, achieve straight morphology, and increase the etching selectivity ratio.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

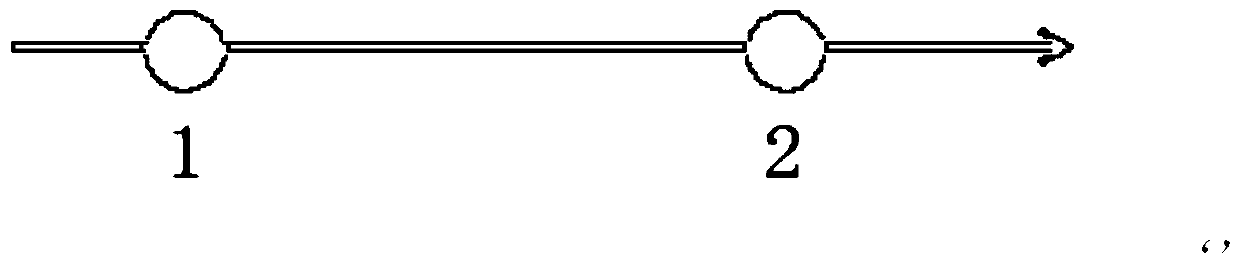

[0028] Such as figure 2 As shown, the present invention provides a first embodiment of a method for improving the morphology of isolation spacers in the production of semiconductor devices, including:

[0029] 1) Deposit the isolation side wall film;

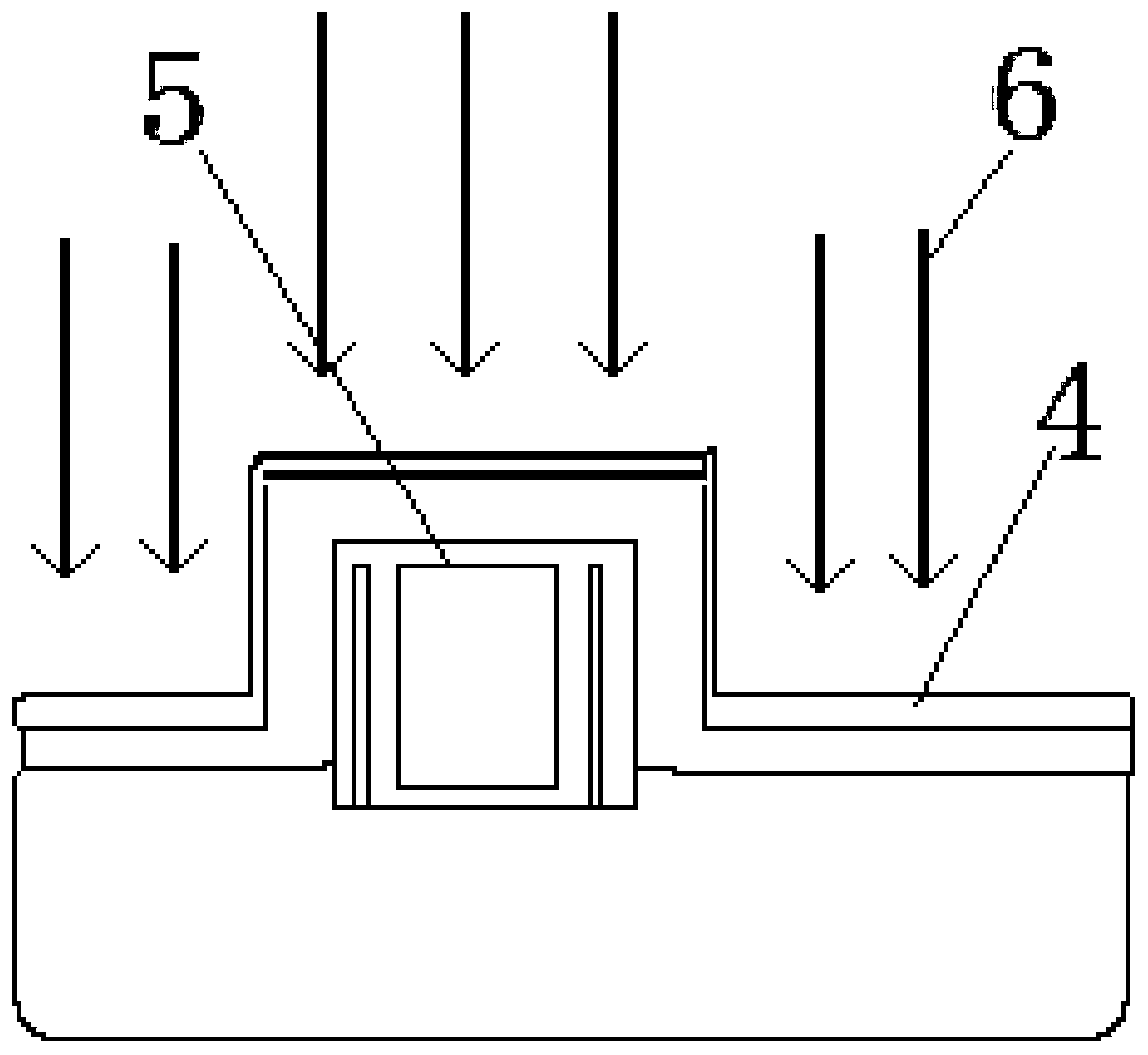

[0030] 2) Perform plasma anisotropic bombardment, the angle of the plasma anisotropic bombardment is vertical bombardment from the top of the device to the bottom, refer to image 3 shown;

[0031] 3) Depositing the isolation side wall film again;

[0032] 4) Then perform isolation spacer etching.

[0033] Wherein, the spacer film is a nitride film, and the plasma is nitrogen, chlorine, hydrogen chloride, bromine or hydrogen bromide.

no. 2 example

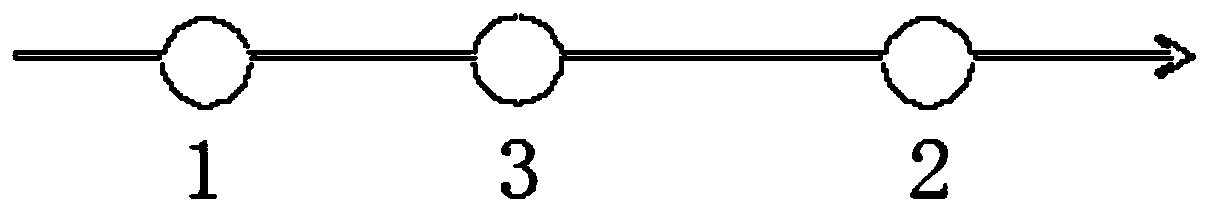

[0034] The present invention provides a second embodiment of a method for improving the morphology of isolation sidewalls in the production of semiconductor devices, including:

[0035] 1) Deposit the isolation side wall film;

[0036] 2) Perform plasma anisotropic bombardment, the angle of the plasma anisotropic bombardment is vertical bombardment from the top of the device to the bottom, refer to image 3 shown;

[0037] Wherein, the plasma anisotropic bombardment pressure is 5mt-10mt, preferably 6mt, 7mt, 8mt or 9mt.

[0038] The power of the plasma anisotropic bombardment source is 400W-700W, preferably 500W or 600W.

[0039] The plasma anisotropic bombardment bias voltage is 100V-200V, preferably 150V.

[0040] 3) Depositing the isolation side wall film again;

[0041] 4) Then perform isolation spacer etching.

[0042] Wherein, the spacer film is a nitride film.

no. 3 example

[0043] The present invention provides a third embodiment of a method for improving the morphology of isolation sidewalls in the production of semiconductor devices, including:

[0044] 1) Depositing an isolation spacer film; the isolation spacer film is a nitride film.

[0045] 2) Perform plasma anisotropic bombardment, the angle of the plasma anisotropic bombardment is vertical bombardment from the top of the device to the bottom, refer to image 3 shown;

[0046] Wherein, the plasma is nitrogen, chlorine, hydrogen chloride, bromine or hydrogen bromide.

[0047] The plasma anisotropic bombardment pressure is 5mt-10mt, preferably 6mt, 7mt, 8mt or 9mt.

[0048] The power of the plasma anisotropic bombardment source is 400W-700W, preferably 500W or 600W.

[0049] The plasma anisotropic bombardment bias voltage is 100V-200V, preferably 150V.

[0050] 3) Depositing the isolation side wall film again;

[0051] 4) Then perform isolation sidewall etching;

[0052] The etching g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com