A screening test method for fpga embedded multiplier

A test method and multiplier technology, which can be used in instruments, simulators, program control, etc., can solve the problems of limited number of packaged I/O ports, complex chip functions, and increased costs, and achieve high test costs and implementation steps. Simplicity, the effect of reducing test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

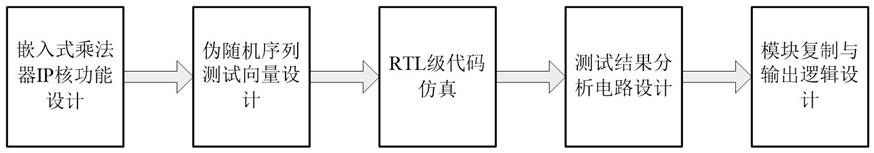

[0022] The performance testing method of the FPGA embedded multiplier of the present embodiment, as figure 1 shown, including the following steps:

[0023] (1) Embedded multiplier IP core function design;

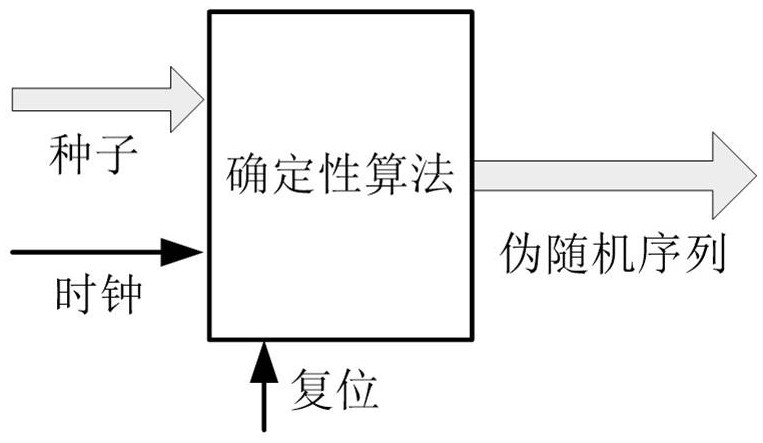

[0024] (2) Pseudo-random sequence test vector design;

[0025] (3) RTL-level code simulation;

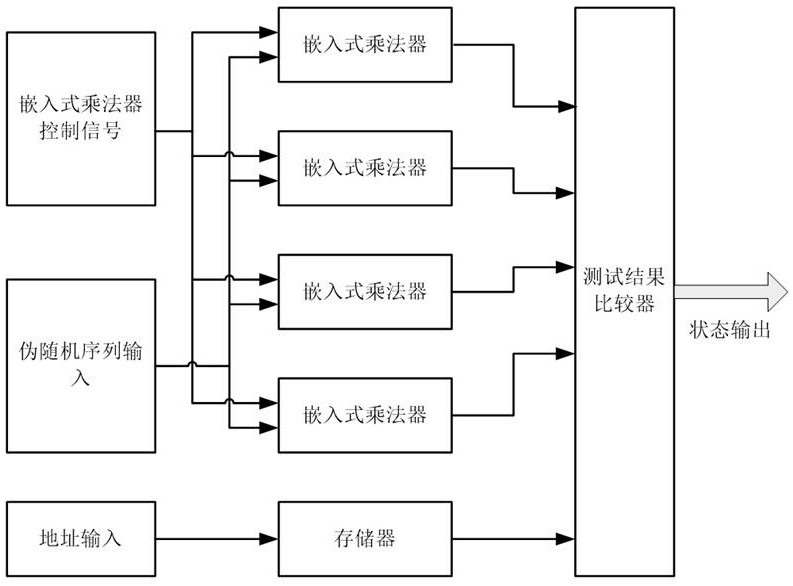

[0026] (4) Test result analysis circuit design;

[0027] (5) Module replication and output logic design.

[0028] The traversal test is a test method that inputs all possible test stimuli to the circuit under test and observes the output results of the circuit under test. If the circuit under test is a combinational logic circuit, assuming that there are n data input pins in total, there are 2n types of test vectors. Assuming that the unit time for each test and completing the observation is t, the total time required to complete the test is 2n·t. For sequential circuits, the total test time will be longer. Therefore, walkthrough testing is generally suitable for circuits ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com