High-speed ARINC429 data processing method based on FPGA

A data processing, high-speed technology, applied in the direction of instruments, computer control, simulators, etc., can solve the problems of waste of CPU processing resources, data loss, high response processing time requirements, etc., to achieve convenient control, simple system interface, and flexible configuration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

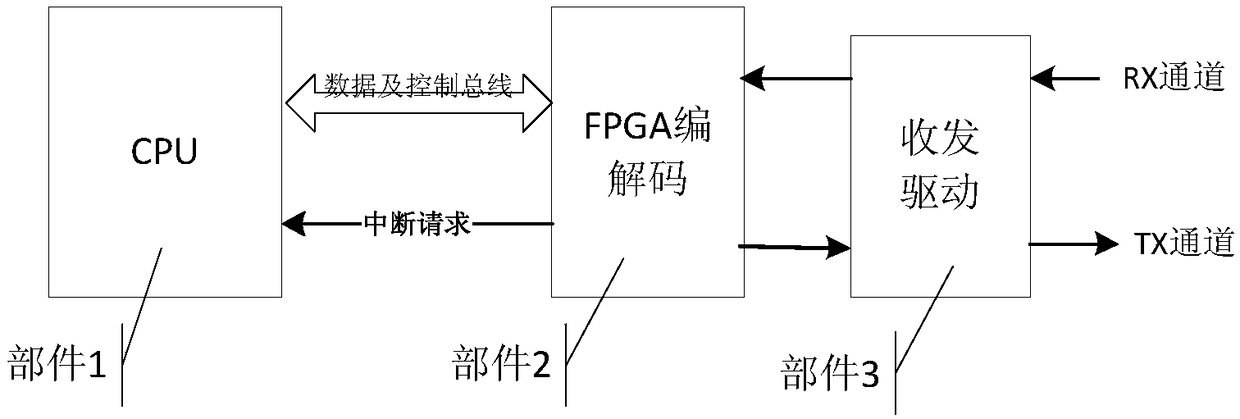

[0028] Aiming at the technical defects of the background technology, the present invention designs a data processing method for high-speed ARINC429 and multi-data conditions with FPGA as the core, utilizes the characteristics of parallel processing and fast processing speed of FPGA to realize hardware filtering, encoding and decoding, etc. , the overall framework is as image 3 shown.

[0029] The functions of each module are as follows:

[0030] 1) Part 1 (CPU): control the channel, rate and sending information of the transmitting code through the bus; control the receiving and decoding rate, parity check, and LABEL number filtering, and at the same time extract the received data from the bus for analysis, and the design uses STM32F746VGT6;

[0031] 2) Component 2 (FPGA codec unit): codec according to the CPU setting, perform LABEL hardware filtering, and design using EP3C120F484I7N;

[0032] 3) Part 3 (transmitting and receiving driver): Convert standard ARINC429 signal to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com