Formation method of three-dimensional memory step structure

A memory and step technology, which is applied in the manufacturing of semiconductor devices, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of non-smoothness, high consumption of photoresist layer, and damage to the step layer.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The specific implementation of the method for forming the three-dimensional memory step structure provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

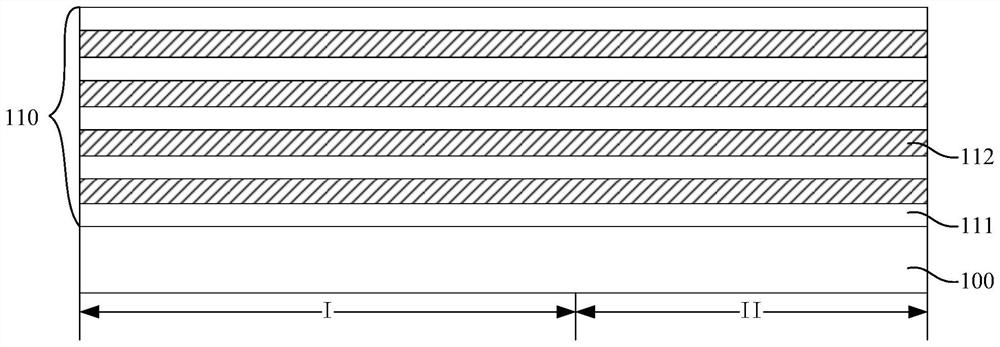

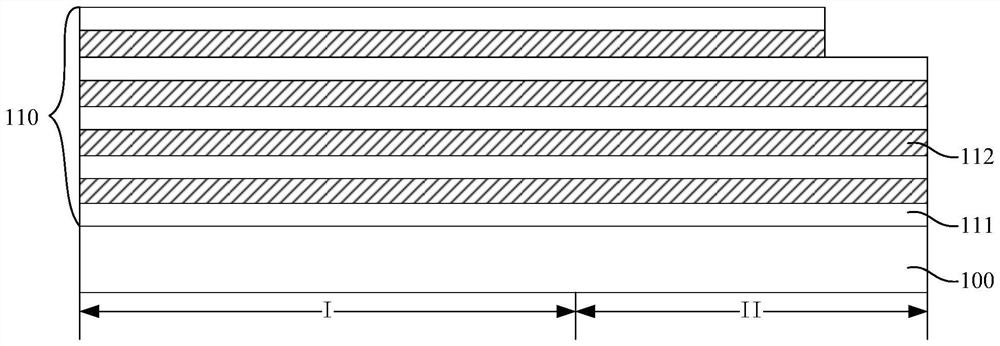

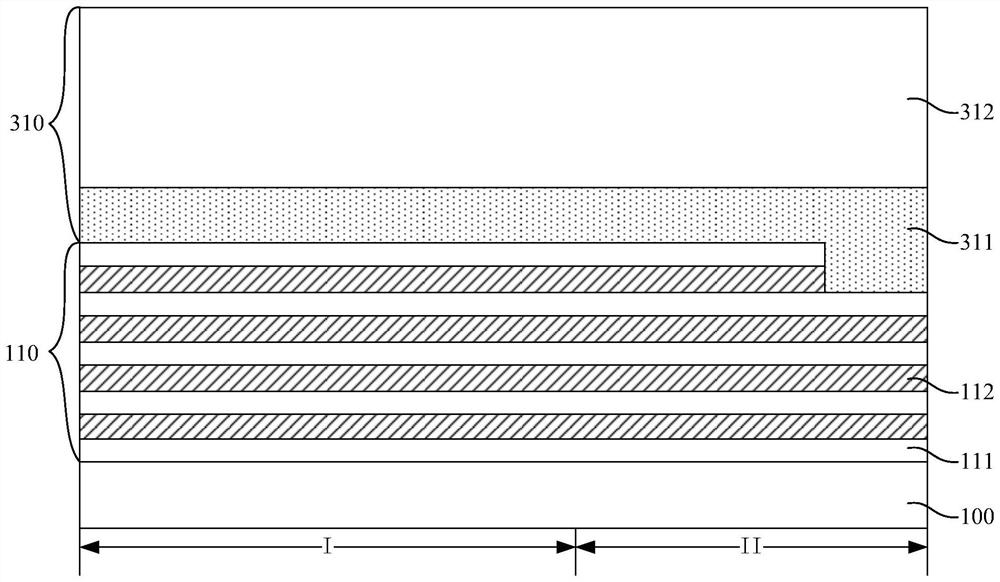

[0024] Please refer to figure 1 , providing a substrate 100 on which a stack structure 110 is formed, and the stack structure 110 includes a core region I and a stepped region II surrounding the core region I.

[0025] The substrate 100 can be a single crystal silicon substrate, a Ge substrate, a SiGe substrate, SOI or GOI, etc.; according to the actual requirements of the device, a suitable semiconductor material can be selected as the substrate 100, which is not limited here. In this specific implementation manner, the substrate 100 is a single crystal silicon wafer.

[0026] The stack structure 110 includes an insulating layer 111 and a sacrificial layer 112 stacked on each other along a direction perpendicular to the surface of the substrate 100 . In a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com