A double-layer vibration isolation structure and preparation method for vibration isolation of mems devices

A vibration isolation and device technology, which is applied in the field of double-layer vibration isolation structure and preparation, can solve the problems of complex active vibration isolation structure, difficult electronic compensation, and increased power consumption of devices, so as to make up for the lack of vibration isolation performance and improve economies of scale , Improve the effect of vibration isolation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

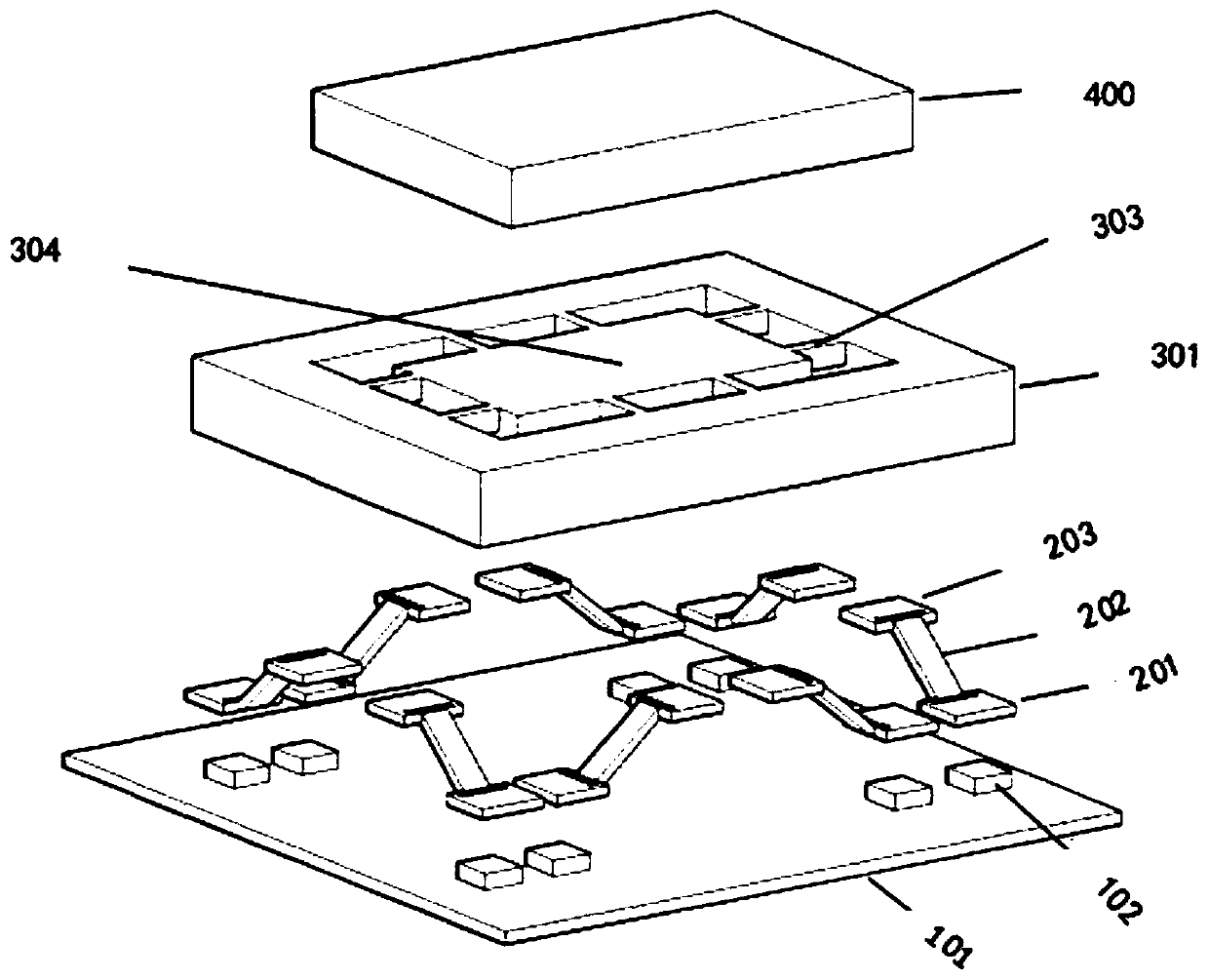

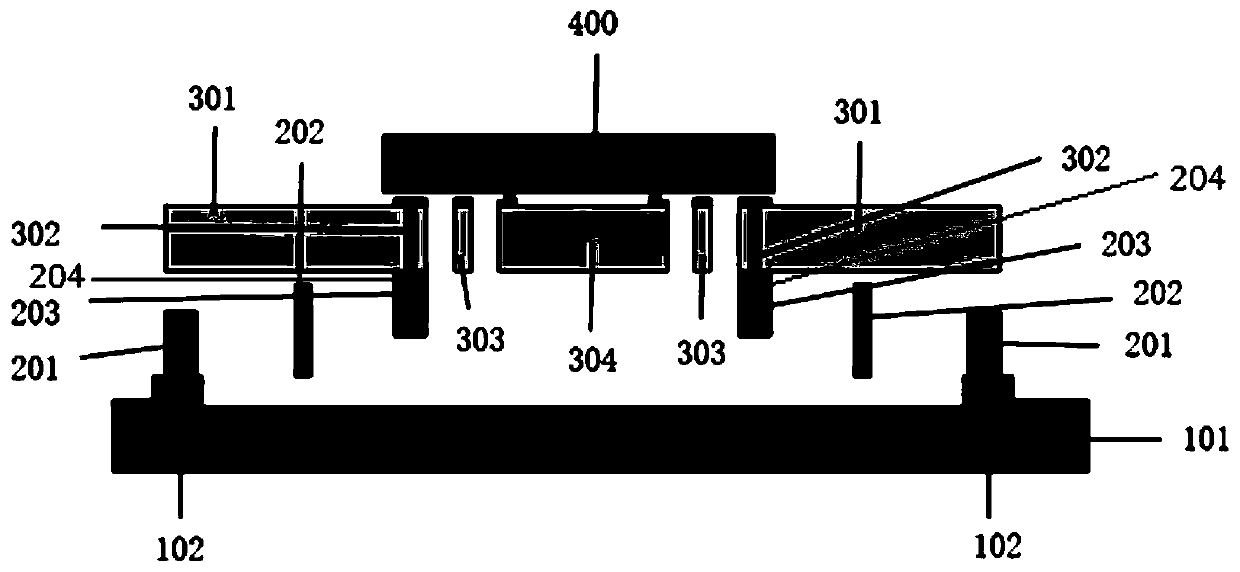

[0049] A double-layer vibration isolation structure for MEMS devices sequentially includes a first-layer vibration isolation system, a second-layer vibration isolation system, and a silicon substrate 101 from top to bottom;

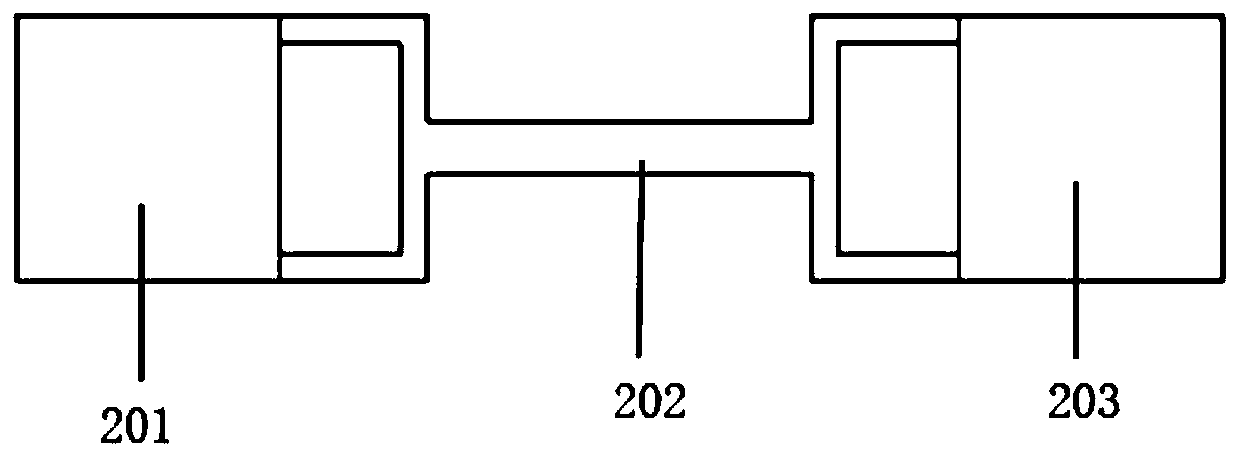

[0050] Such as figure 1 combine figure 2 , Figure 4 As shown, the first layer of vibration isolation system includes a connection frame 301, a vibration isolation platform 304 and several vibration isolation beams 303; the connection frame 301 is surrounded by the vibration isolation platform 304, and several vibration isolation beams 303 are connected between the connection frame 301 and the vibration isolation platform 304; the connection frame 301 is provided with a first through hole 302 close to each vibration isolation beam 303, and a through hole lead is provided in the first through hole 302; an insulating layer is provided on the upper surface of the vibration isolation beam 303, and the insulating layer Metal leads are provided on the top; t...

Embodiment 2

[0069] The steps of preparing a double-layer vibration isolation structure for vibration isolation of MEMS devices are as follows:

[0070] (1) Prepare slices: prepare a 475 μm thick double-sided polished silicon substrate 305, a 500 μm thick glass slice 306, and a 500 μm thick silicon substrate 101;

[0071] (2) The first photolithography: such as Figure 5 As shown, the double-sided polished silicon substrate 305 is cleaned with deionized water, the cleaned double-sided polished silicon substrate 305 is spin-coated with a layer of photoresist, and the mask plate is used for inductively coupled plasma (ICP) etching , etch a shallow step with a height of 3-4 μm;

[0072] (3) Silicon glass bonding: such as Image 6 As shown, the side of the silicon substrate 305 etched in step 2 with a shallow step is bonded to the glass sheet 306 in step 1 by bonding technology;

[0073] (4) The second photolithography: if Figure 7 As shown, the upper pad 203, the second through hole 204,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com