Memory cells, methods of forming an array of two transistor-one capacitor memory cells, and methods used in fabricating integrated circuitry

A technology of memory cells and capacitors, applied in the direction of capacitors, transistors, circuits, etc., can solve problems such as incorporation and difficult capacitors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

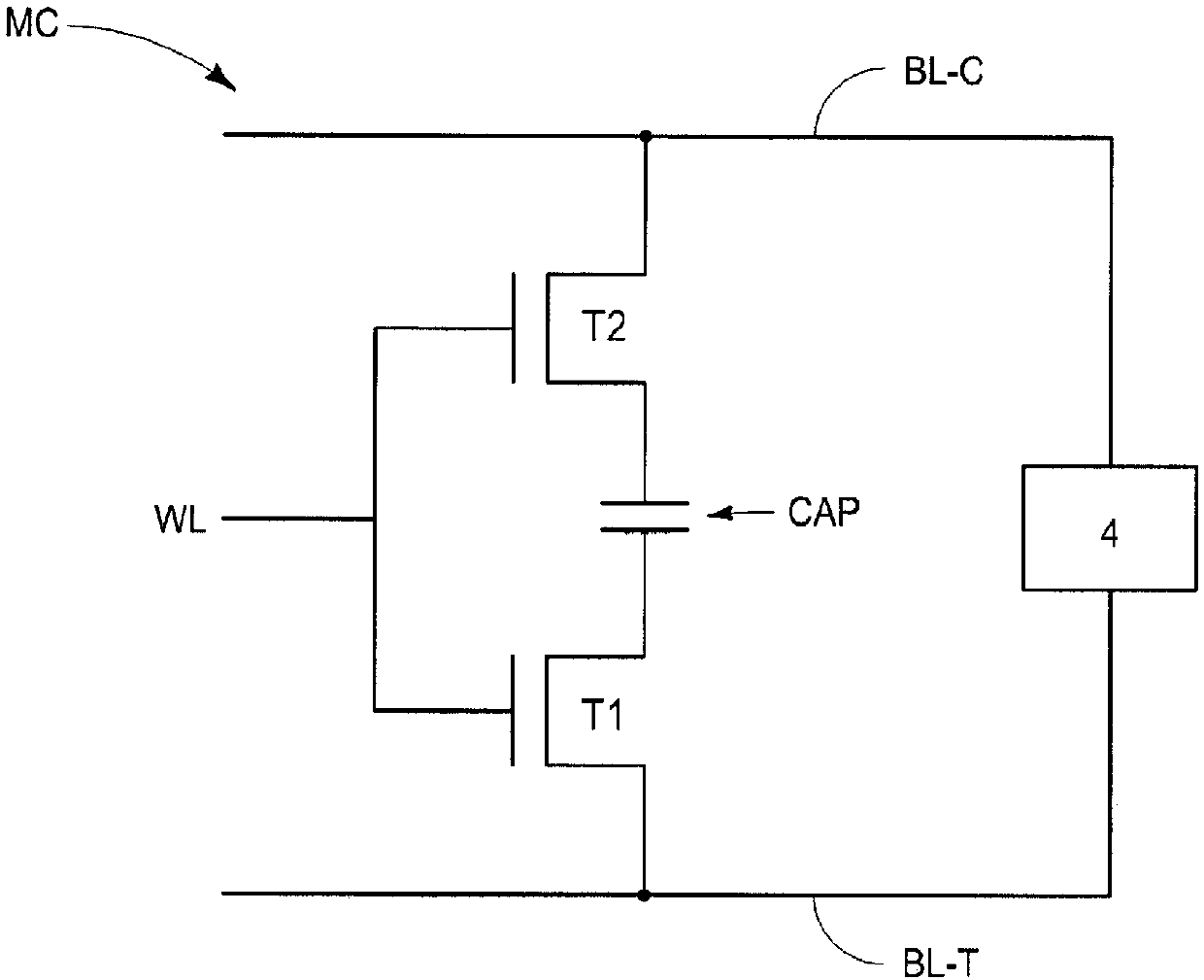

[0033]Embodiments of the invention include memory cells that are independent of fabrication methods. Embodiments of the invention also include methods of forming arrays of two transistor one capacitor (2T-1C) memory cells and methods for fabricating integrated circuits. While not in every way being so limited, the provided drawings depict fabrication methods and structures associated with 2T-1C memory cells, such as shown schematically in FIG. 1 . An example 2T-1C memory cell MC has two transistors T1 and T2 and a capacitor CAP. A source / drain region of T1 is connected to a first conductive node of capacitor CAP, and another source / drain region of T1 is connected to a first comparison bit line (eg, BL-T). The gate of T1 is connected to the word line WL. The source / drain region of T2 is connected to the second conductive node of the capacitor CAP, and the other source / drain region of T2 is connected to the second comparison bit line (eg, BL-C). The gate of T2 is connected to...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap