Microphone array signal processing system and method

A microphone array and signal processing technology, which is applied in the direction of electrical digital data processing, transducer circuits, instruments, etc., can solve the problems of inflexible application, high cost, and complex system, so as to improve processing efficiency, improve receiving speed, and apply broad effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

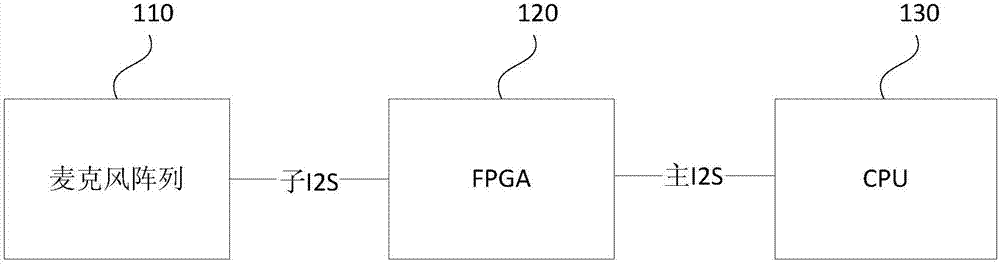

[0037] figure 1 It is a structural block diagram of a microphone array signal processing system provided in Embodiment 1 of the present invention. like figure 1 As shown, the system includes: FPGA120, CPU130, main I2S, sub-I2S and microphone array 110, wherein:

[0038] The microphone array 110 is used to obtain the first analog audio data in the environment, and convert the first analog audio data into the first digital audio data, and send it to the FPGA 120; the FPGA 120 is connected to the microphone array 110 through a sub-I2S, and is used to receive the The first digital audio data of at least one path sent by the array 110, and the first digital audio data are sent to the CPU 130; the CPU 130 is connected to the FPGA through the main I2S, and is used to receive the first digital audio data sent by the FPGA 120, and send the first digital audio data to the CPU 130; The digital audio data is filtered and denoised to obtain the second digital audio data; wherein, the mai...

Embodiment 2

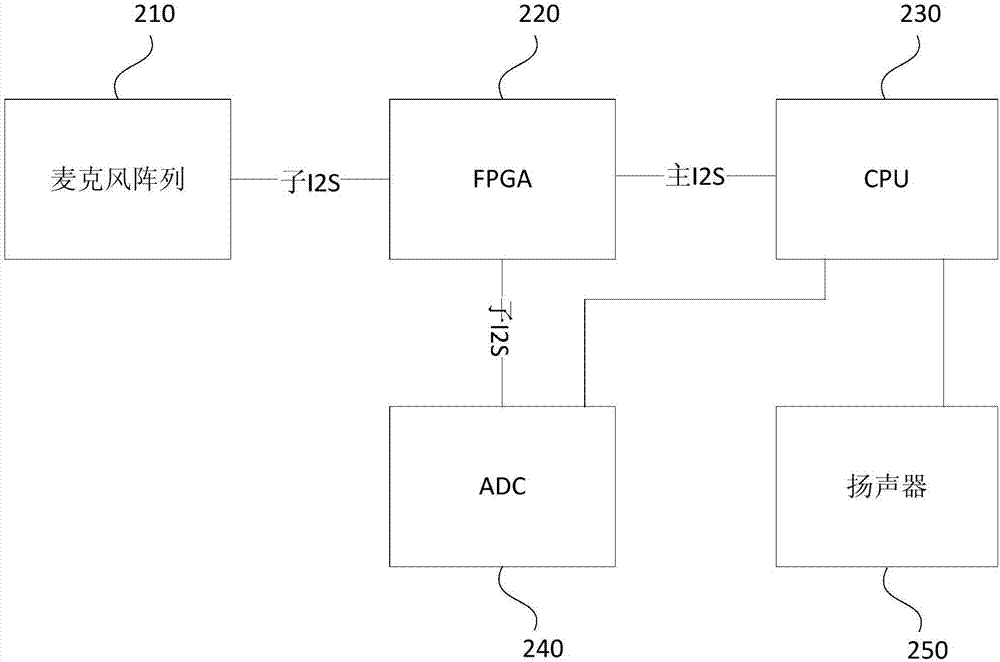

[0045] figure 2 It is a structural block diagram of a microphone array signal processing system provided in Embodiment 2 of the present invention. On the basis of the above embodiments, an ADC and a loudspeaker are added, a noise reduction signal is introduced, and the CPU data processing speed is improved. The system includes: FPGA 220, CPU 230, main I2S, sub I2S, microphone array 210, ADC 240 and speaker 250, wherein:

[0046] The CPU 230 is also used to: convert the second digital audio data into second analog audio data, and send the second analog audio data to the ADC 240 and the speaker 250;

[0047] ADC 240, connected with CPU 230 and FPGA 220, for obtaining the second analog audio data sent by CPU 230, and converting the second analog audio data into third digital audio data, and sending the third digital audio data to FPGA220, The FPGA 220 aggregates the third digital audio data and the first digital audio data and sends them to the CPU 230;

[0048] The speaker i...

Embodiment 3

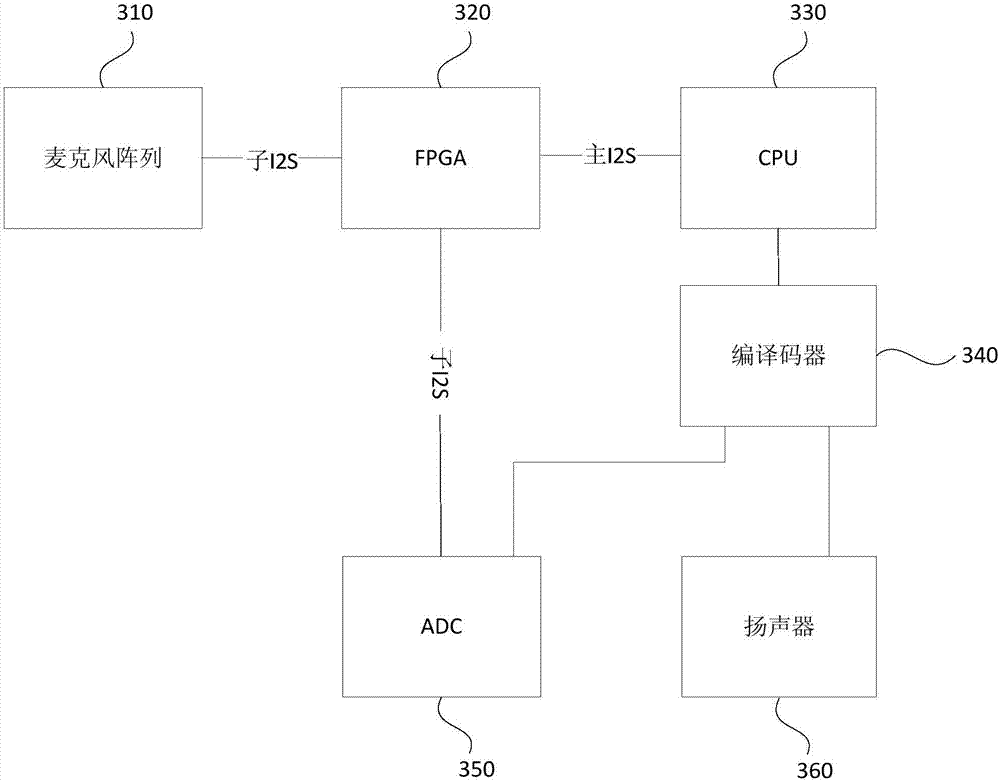

[0056] image 3 It is a structural block diagram of a microphone array signal processing system provided by Embodiment 3 of the present invention. On the basis of the above embodiments, the output of the system analog signal is specifically optimized. The system includes: FPGA320, CPU330, main I2S, sub-I2S, microphone array 310, codec 340, ADC350 and loudspeaker 360, wherein:

[0057] A codec 340, connected to the CPU 330, receives the second digital audio data sent by the CPU 330, decodes the second digital audio data, obtains the third analog audio data, and sends the third analog audio data to the ADC 350 and the speaker 360;

[0058] The ADC 350 is connected to the codec 340 and the FPGA 320, and is used to acquire the third analog audio data sent by the codec 340, convert the third analog audio data into fourth digital audio data, and send the fourth digital audio data For the FPGA 320, the FPGA 320 is used to gather the fourth digital audio data and the first digital a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com